C.Ю. Фарафонтов

Основы конструирования электронных средств

Учебно-методическое пособие

Новосибирск

2019

УДК 000.(000)

Утверждено редакционно-издательским советом СибГУТИ

Рецензент канд. техн. наук, доц. А.А. Петров

Фарафонтов С.Ю. Основы конструирования электронных средств: Учебно-методическое пособие / Сибирский государственный университет телекоммуникаций и информатики; каф. радиотехнических устройств. – Новосибирск, 2019. – 37 с.

В данном учебно-методическом пособии приведено описание лабораторного практикума, предназначенного для бакалавров и магистров различных профилей в области телекоммуникаций, бакалавров и магистрантов по специальности 11.03.03(02) «Конструирование и технология электронных средств».

Лабораторные работы выполняются на специализированных стендах с программируемой логической интегральной микросхемой (ПЛИС) ЕР1С3Т144С8 учебный стенд LESO2. Процесс синтеза устройств происходит за счет загрузки в память ПЛИС определённых конфигурационных файлов, что дает возможность на одном и том же оборудовании разрабатывать разные по логике работы устройства.

© Фарафонтов С.Ю., 2019

© Сибирский государственный университет

телекоммуникаций и информатики, 2019

Лабораторная работа №1

Исследование двоичных логических элементов

Цель работы

Целью работы является изучение способов создания основных двоичных логических элементов на языке Verilog для ПЛИС Altera Intel.

Система автоматизированного проектирования Quartus II.

2.1 Создание проекта

Разработка конфигурационного файла программируемой интегральной микросхемы (далее ПЛИС) на основе языка описания аппаратуры Verilog производится в среде Quartus II для ПЛИС производства Altera Intel. Для создания проекта требуется создать папку для хранения файлов проекта. Имя папки, а также путь нахождения папки не должен содержать символы кириллического алфавита. Затем следует запустить программу Quartus II. Далее выбираем из меню File раздел New Project Wizard. В открывшемся окне мастера создания проектов нажимаем кнопку Next и попадаем в окно для указания пути к папке проекта и имени проекта. Следует отметить, что имя проекта может быть любым, но не содержать символы кириллического алфавита. После заполнения полей окна следует нажать кнопку Finish. Проект создан.

2.2 Создание файла Verilog

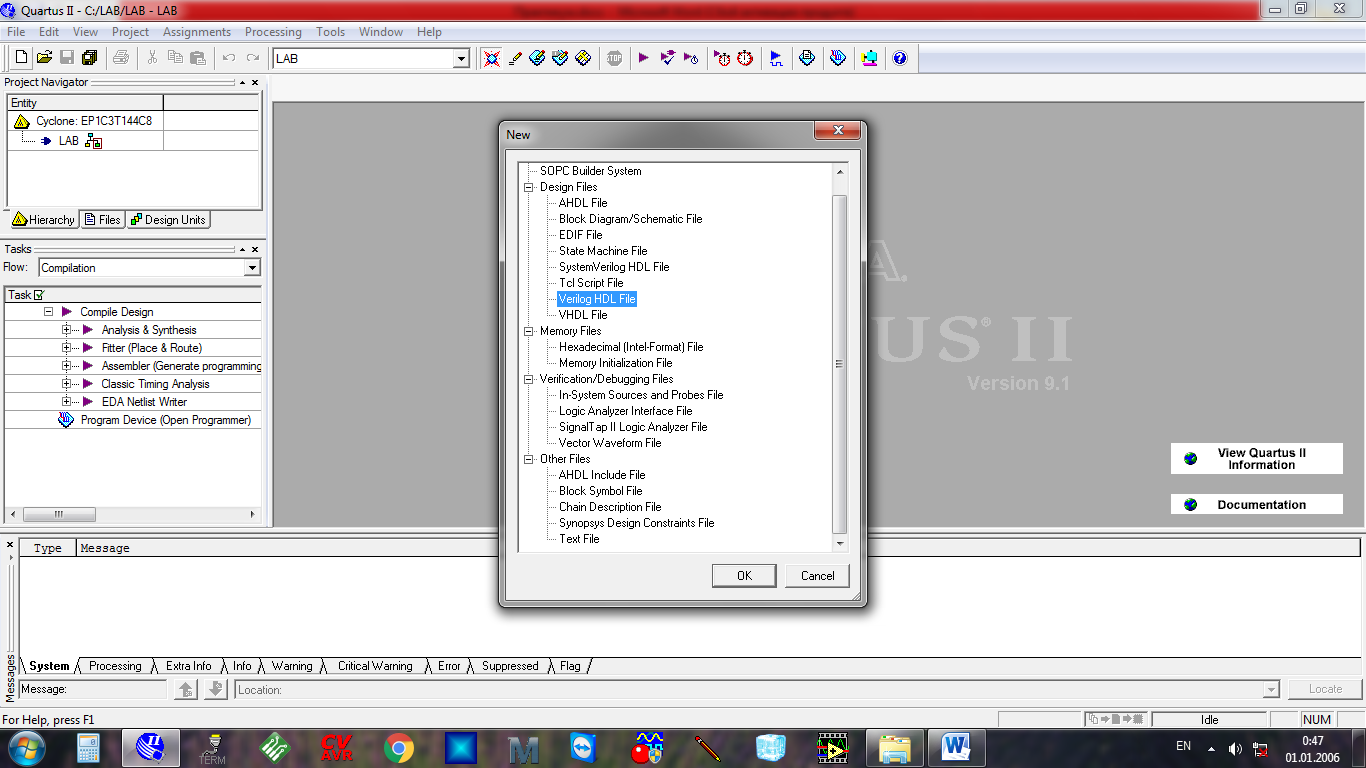

Разработка логической функции, определяющая логику работы ПЛИС, производится на основе языка описания аппаратуры Verilog. Для описания алгоритма на языке Verilog следует создать рабочий файл. Для этого в меню File следует выбрать раздел New, где в выпавшем окне следует выбрать пункт Verilog HDL File и нажать кнопку ОК (рисунок 2.1).

Рис. 2.1. Выбор типа файла проекта

2.3 Создание алгоритма на языке Verilog

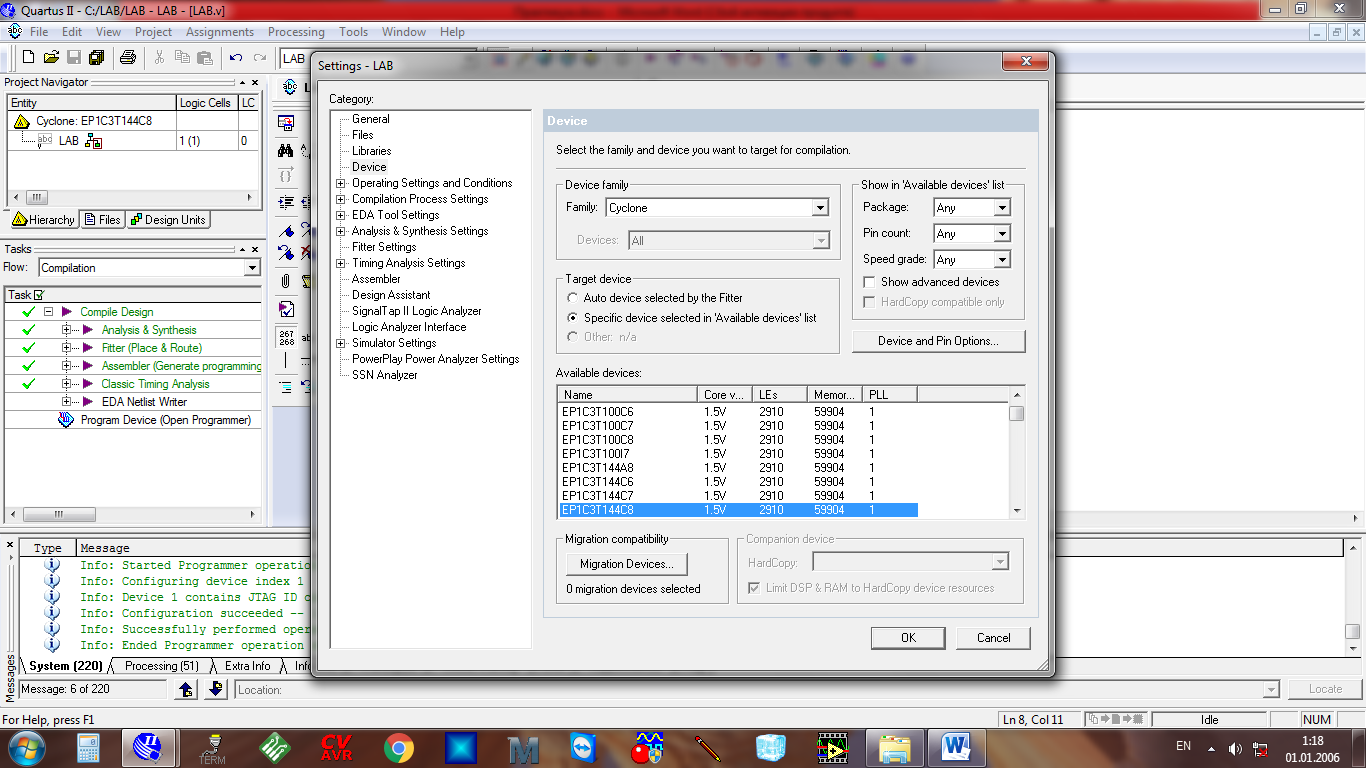

Создадим алгоритм реализующий логическую функцию элемента «И». При этом зададимся, что при создании проекта проекту было присвоено имя «LAB». Перед написанием алгоритма требуется произвести выбор типа ПЛИС. Для этого следует зайти в меню настройки проекта Settings. В открывшемся окне следует выбрать раздел Device. В списке имен семейств ПЛИС (Список Device Family) выбрать Cyclone. Далее в таблице Available devices выбрать ПЛИС ЕР1С3Т144С8 (рисунок 2.2). Затем закройте окно нажав на кнопку ОК.

Перейдем в ранее созданный файл проекта Verilog и напишем следующий алгоритм:

module LAB (X1, X2, Y);

input wire X1;

input wire X2;

output wire Y;

assign Y = X1 & X2;

endmodule

Далее произведем копиляцию созданного проекта. Для этого следует нажать на кнопку Start Compilation, расположенной на верхней панеле.

Рис. 2.2. Выбор ПЛИС

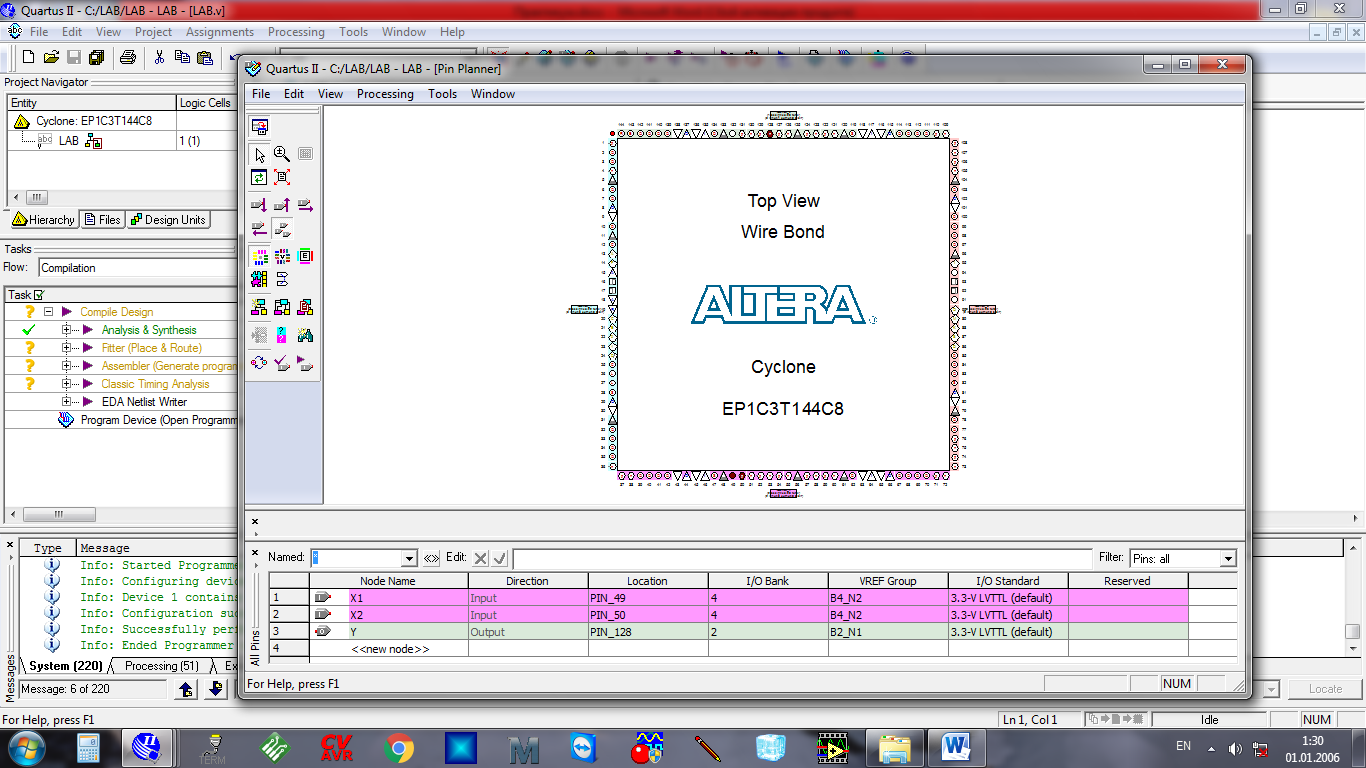

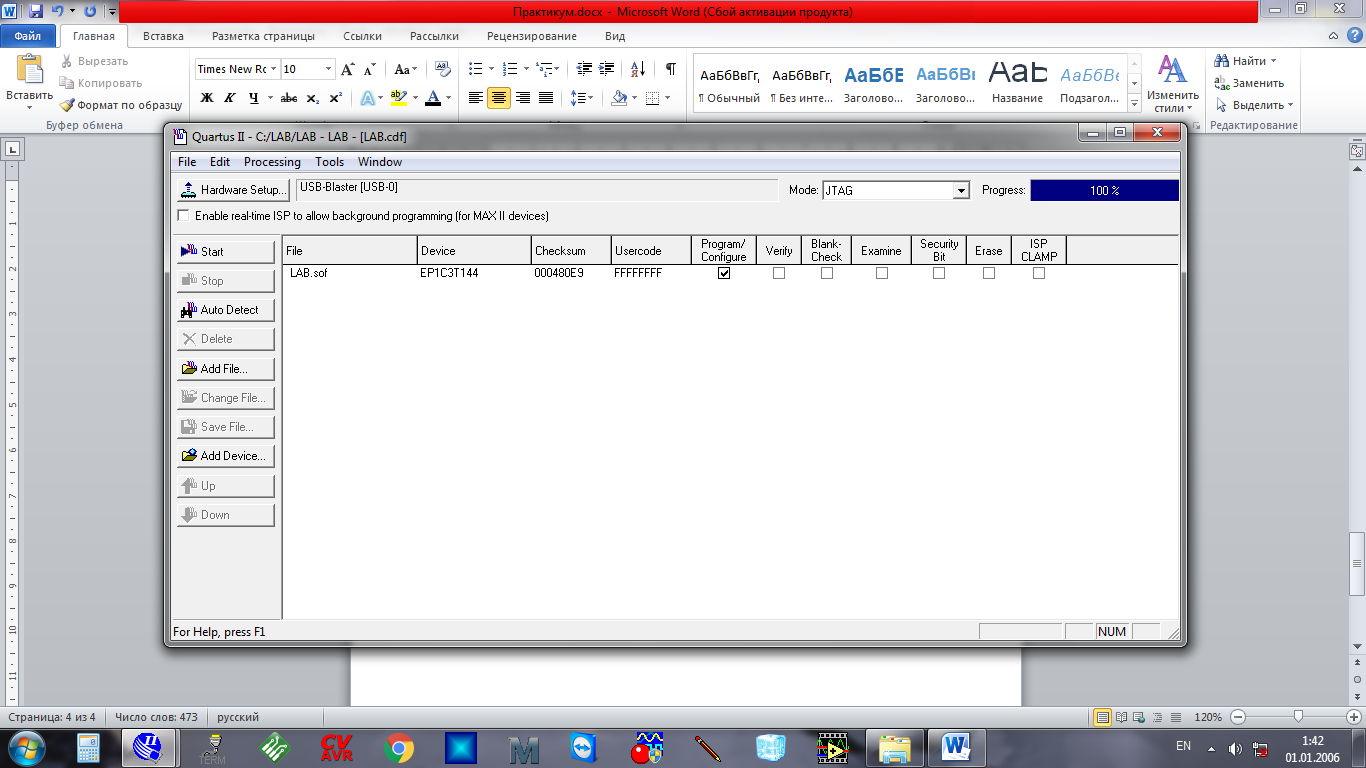

После завершения компиляции и отсутствия ошибок в нижнем окне Messages. Следует назначить номера входных и выходного порта. Для этого следует нажать на кнопку Pin Planner, расположенную на верхней панели. В открывшемся окне, в нижней таблице укажем, что вывод «Х1» нужно подключить к 49 выводу ПЛИС, вывод «Х2» нужно подключить к 50 выводу ПЛИС, вывод «У» следует подключить к выводу 128 (рисунок 2.3). Далее закрываем окно и повторно компилируем проект. После успешной компиляции следует произвести загрузку конфигурационного файла в ПЛИС. Для этого подключаем учебный стенд и программатор USB Blaster к ПЭВМ. Далее нажимаем на кнопку Programmer, расположенную на верхней панели. В открывшемся окне нажимаем на кнопку Hardware Setup. В раскрывающемся списке Currently selected hardware выбираем программатор USB Blaster. И нажимаем кнопку Close. Далее следует нажать на кнопку Start, что приведет к загрузке конфигурационного файла в ПЛИС (рисунок 2.4).

Рис. 2.3. Задание номеров используемых выводов ПЛИС

Рис. 2.4. Окно мастера загрузки конфигурационного файла в ПЛИС

2.4 Исследование созданного алгоритма

После загрузки конфигурационного файла в ПЛИС переведите переключатели S1 и S2 в нижнее положение. При этом светодиод LED1 светиться не будет. Далее переведите оба переключателя S1 и S2 в верхнее положение. При этом светодиод LED1 включится. При этом перевод только одного из двух переключателей S1 и S2 в верхнее положение не приведет к включению светодиода LED1. Как это работает?

При создании файла Verilog мы объявили два входных порта «Х1», «Х2» и один выходной порт «Y». При этом в настройках портов мы указали, что порт «Х1» подключатся к 49 выводу ПЛИС. Порт «Х2» подключается к 50 выводу ПЛИС. Порт «У» подключается к 128 выводу ПЛИС. К 49 и 50 выводам ПЛИС подключаются переключатели S1 и S2 формирующие на данных выводах уровень логической единицы в верхнем положении движков переключателей и уровень логического нуля при нижнем положении. К 128 выводу ПЛИС подключен светоизлучающий диод LED1, который включается (начинает излучать свет) при наличии на данном выводе уровня логической единицы.

Далее в созданном модуле LAB мы указали, что в порт «Y» следует записать результат логической операции «И» между портами «Х1» и «Х2»:

assign Y = X1 & X2;

где assign – оператор для непрерывного присвоения;

Y – выходной порт;

X1 – входной порт;

& – логический оператор функции «И»;

X2 – входной порт.

Поэтому, исходя из таблицы истинности логической операции «И» в порт «Y» запишется логическая единица только тогда, когда на обоих входных портах «Х1» и «Х2» будут присутствовать логические единицы.

Задание к работе

По аналогии с логической функцией «И» произведите исследование функционирования логических операторов, приведенных в таблице 3.1. Результаты исследований свести в таблицу.

Табл. 3.1. Логические операции

| № | Исполняемая функция | Обозначение |

| 1 | И | & |

| 2 | ИЛИ | | |

| 3 | НЕ | ! |

| 4 | Исключающее ИЛИ | ^ |

| 5 | Исключающее ИЛИ-НЕ | ~^ |

Содержание отчета

4.1 Цель работы.

4.2 Алгоритм модуля на языке Verilog для каждого логического элемента.

4.3 Таблицы истинности исследуемых логических функций.

4.4 Вывод

Контрольные вопросы

5.1 Что такое ПЛИС?

5.2 Какие преимущества дает проектирование аппаратуры на ПЛИС?

5.3 Что такое файл конфигурации?

5.4 Этапы создания проекта с помощью программы Quartus II.

5.5 Как производится объявление портов на языке Verilog?

5.6 Как производится назначение объявленным портам номеров выводов ПЛИС?

5.7 Как устроен лабораторный стенд?

5.8 Запишите логические выражения на языке Verilog для исследованных логических функций.

5.9 Что такое таблица истинности?

5.10 Изобразите таблицы истинности основных логических элементов.

2020-07-12

2020-07-12 208

208