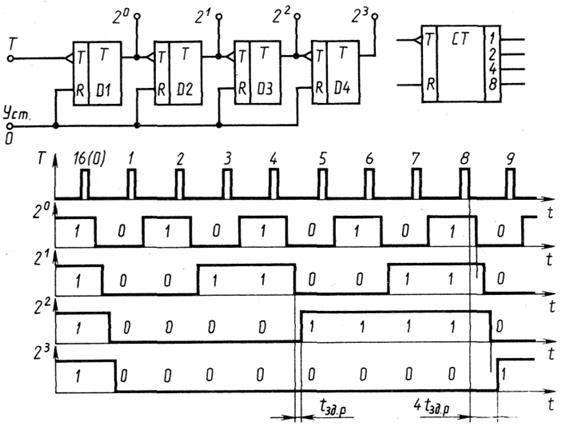

Асинхронный (последовательный) двоичный счетчик образован цепочкой последовательно включенных счетных триггеров. Результат счета отображается на выходах счетчика Q(N —1),..., Q 0 в виде параллельного двоичного кода числа сосчитанных импульсов. Поскольку число выходных переменных равно числу триггеров N и каждая переменная может принимать лишь два значения, то число возможных состояний (коэффициент счета) равно Ксч =2 N. Так как из 2 N состояний одно приходится на нулевое состояние, то максимальное число, при котором счетчик полностью заполняется единицами, равно (2 N -1).

Простейшим одноразрядным счетчиком с Ксч =2 N является Т -триггер, меняющий свое состояние на противоположное под действием каждого входного сигнала. В результате перепады напряжения на выходе триггера имеют вдвое меньшую частоту, чем на входе. По этим перепадам запускается следующий триггер, и на его выходе изменения состояния происходят уже в четыре раза реже, чем на входе первого триггера.

В соответствии с рисунком 102 изображены четырехразрядный двоичный счетчик на Т-триггерах, срабатывающих по срезу входного сигнала.

Задержки распространения импульса в каждом триггере могут привести к искажению информации в счетчике и потому многоразрядные счетчики с последовательным переносом счетных импульсов от триггера к триггеру могут работать только на пониженных частотах, при достаточно больших периодах следования импульсов.

Кроме суммирующего счетчика, имеются и вычитающие счетчики, у которых выходной код уменьшается на 1 с приходом каждого счетного импульса. Такой счетчик получится при подаче инверсных сигналов на тактовые входы.

Для этого необходимо тактовые входы триггеров подключить к инверсным выходам  предыдущих триггеров.

предыдущих триггеров.

Рисунок 102

Если в состав счетчика ввести мультиплексор, переключающий тактовые входы триггеров к прямым или инверсным выходам предыдущих триггеров, мы получим реверсивный счетчик с изменяемым направлением счета.

Арифметическо-логические узлы

Сумматор

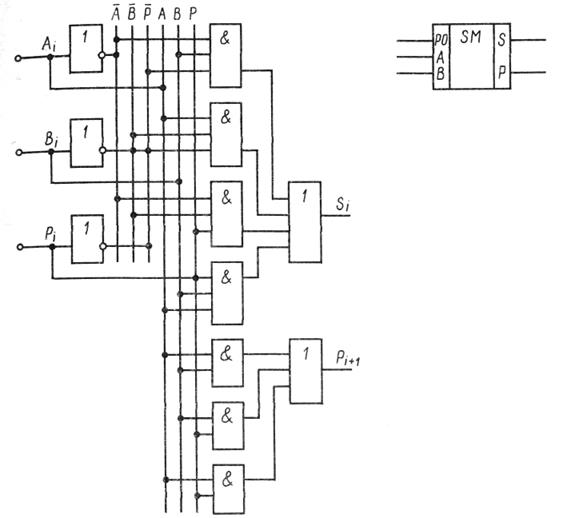

Сумматор предназначен для арифметического сложения двух чисел. При сложении двух многоразрядных двоичных чисел в каждом i -м разряде находится сумма трех чисел по модулю два (слагаемые Аi, Вi и перенос, поступивший из младшего разряда Рi) и формируется сигнал переноса в старший разряд  . Таблица 6 (таблица истинности) для одноразрядного сумматора приведена ниже.

. Таблица 6 (таблица истинности) для одноразрядного сумматора приведена ниже.

Таблица 6

Символическое изображение одноразрядного сумматора приведено В соответствии с рисунком 103.

Рисунок 103

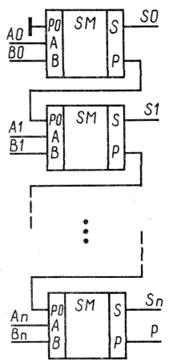

Для сложения двух многоразрядных двоичных чисел используют многоразрядные сумматоры, представляющие собой в простейшем виде последовательное соединение одноразрядных сумматоров в соответствии с рисунком 104.

Рисунок 104

Есть микросхемы одно-, двух- и четырехразрядные сумматоры, которые можно объединить для получения сумматоров с любой разрядностью. Бывают сумматоры с параллельным поразрядным сложением и последовательным формированием сигнала переноса. Для повышения быстродействия создают схемы сумматоров с параллельным переносом, принцип построения которых подобен построению счетчиков со сквозным переносом (синхронные счетчики).

2020-08-05

2020-08-05 280

280