Переведите ИМС рис. 10.43 в режим однократного счета и определите время задержки Тзд формирования на ее выходе положительного фронта сигнала 0→1 по отношению к моменту поступления первого счетного импульса. При расчете примите частоту входных сигналов fвх равной 0,5 МГц, а Кя = 16977.

98

Контрольные вопросы

3(1)

Глава 10

99

Контрольные вопросы к главе 10

|

|

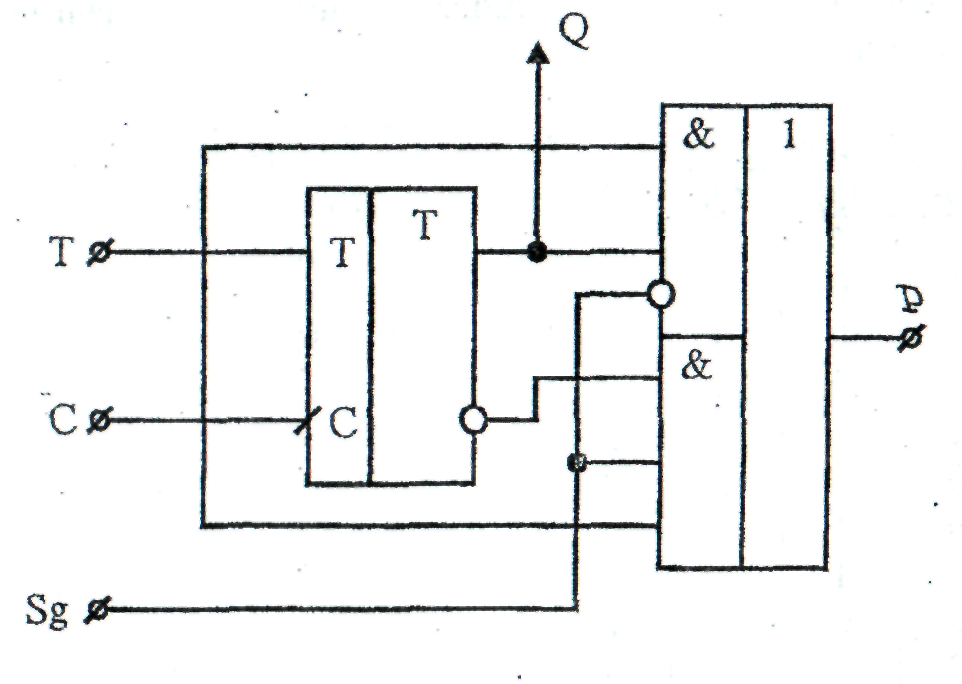

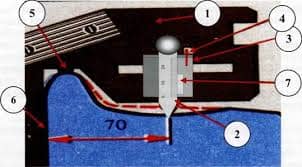

1. Определите назначение схемы, приведенной на рисунке, напишите уравнения, описывающие процесс формирования сигналов на выходе Q в момент времени (t+1) и на выходах Рс и Рв в момент времени t.

| 0 Pc(CRU) |

| ^ Pb(CRD) |

2. Назовите основные преимущества и недостатки счетчиков с последовательным переносом.

3. Определите к какому типу пересчетных ячеек относится схема, представленная на рисунке. Запишите логические уравнения для сигналов Q(t+1) и P(t), формируемых на выходах схемы в указанные моменты времени.

|

|

101

4. Какие существуют разновидности счетчиков при их классификации по методам организации цепей переноса (займа) между разрядами?

5. Кратко охарактеризуйте основные методы задания коэффициента деления частоты Кдел. в регулируемых (программируемых) делителях.

6. Объясните назначение отдельных элементов графа переходов счетчика.

7. Чему равен коэффициент деления частоты Кдел.р, при параллельном включении делителей, выходы которых подключают ко входам логического элемента И, формирующего выходную последовательность сигналов?

8. В каком случае коэффициент деления Кдел. делителя частоты должен определяться из соотношений:

• КДЕЛ= K1·K2·...·KN?

•• Кдел= (К1·К2 ·…·KN)-Kо.д ?

• • • Кдел. = Кдел. р.· Кдел.. s

где K1, К2,..., Kn - коэффициенты деления отдельных делителей частоты; Ко.д. - общий делитель для коэффициентов K1, К2,..., КN; Кдел.р. - коэффициент деления параллельной группы делителей; Кдел.s - тоже для последовательной группы делителей частоты.

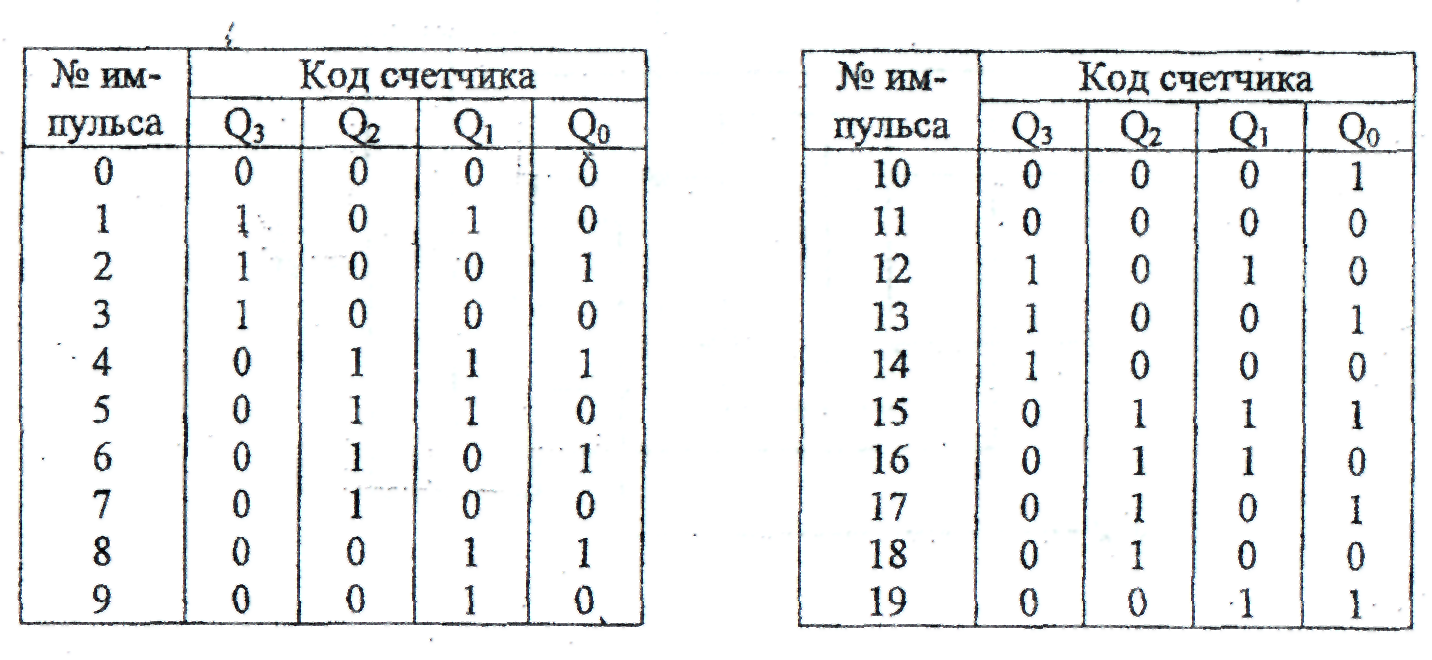

9. Из представленной ниже таблицы истинности определите тип счетчика и его модуль счета К.

|

|

102

'10. Приведите пример КМОП ИМС счетчика, использующего кодирование его состояний в соответствии с представленной ниже таблицей.

|

|

11. Что обозначает надпись СТ2 /СТ10 в центральном поле условного графического обозначения счетчика?

12. Что представляют собой следующие ИМС счетчиков:

• КА561ИЕ15А (КА561ИЕ15Б)?

••КР531ИЕ14?

••• КР1533ИЕ12?

••••К561ИЕ16(ЭКФ561ИЕ16)?

••••• К561ИЕ19?

13. Как следует понимать термин «асинхронный» по отношению к счетчикам импульсов?

14. • Какое число является конечным в 4-разрядном реверсивном двоичном счетчике в режиме суммирования?

•• В режиме вычитания?

••• Какое число является следующим после конечного в режиме вычитания?

•••• В режиме суммирования?

15. Какие электронные схемы принято называть

• Счетчиками импульсов?

•• Делителями частоты?

103

16. В каком соотношении друг с другом находятся максимальная частота счета fms счетчика с последовательным переносом и максимальная частота счета fmp, с параллельным переносом?

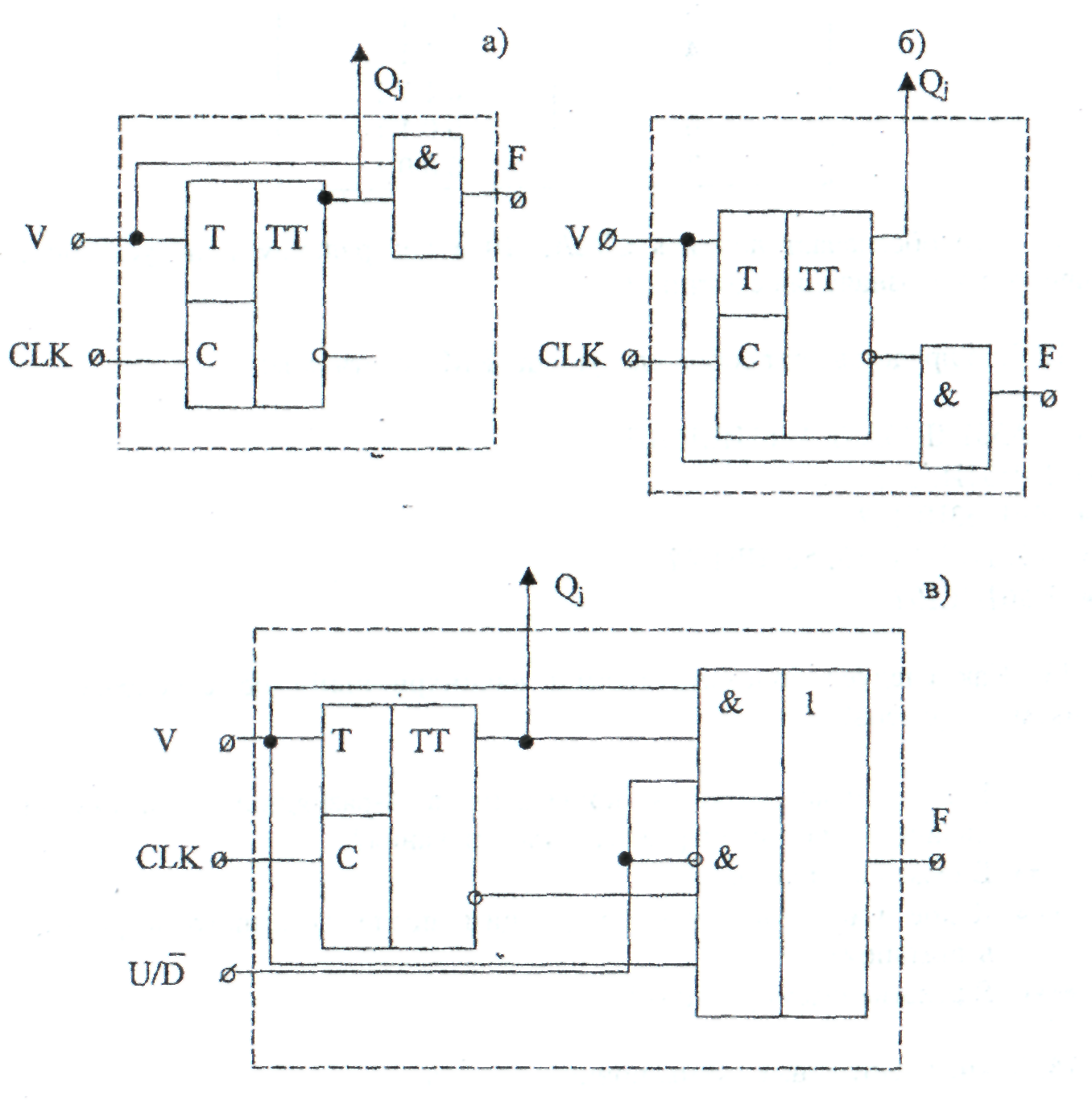

17. На представленных ниже рисунках (а), (б) и (в) приведены схемы одноразрядных счетчиков. Определите какому типу счетчиков они могут принадлежать.

|

|

18. Раскройте рекуррентное логическое уравнение (10.42) для вычитающего синхронного счетчика со сквозным переносом в виде последовательной цепочки равенств относительно сигнала переноса (займа) Tj+1.

104

19. Зависит ли модуль счета двоичного счетчика и его таблица переключений (граф переходов) от способа организации переноса?

20. Каким образом может быть рассчитано разрешающее время Тр счетчика с последовательным переносом при следующих вариантах его реализации:

• Суммирующий счетчик;

•• Вычитающий счетчик;

• •• Реверсивный счетчик.

21. Что понимают под разрешающим временем счетчика и его максимальной частотой счета?

22. Чему равно время установки кода счетчика?

23. Каково происхождение аббревиатуры «СТ» в обозначении счетчика?

24. На основе анализа временных диаграмм рис. 10.44 выполните следующие операции:

• Запишите кодовые комбинации {Q1, Q2, Q0}, реализуемые на выходах счетчика до начала счета и после поступления каждого счетного импульса;

•• Определите модуль счетчика К;

•••Рассчитайте частоту сигналов f0,,f1,,f2 на выходах счетчика Q0, Q1 и Q2 соответственно, если частота входных импульсов fвх равна 1МГц.

|

|

105

|

|

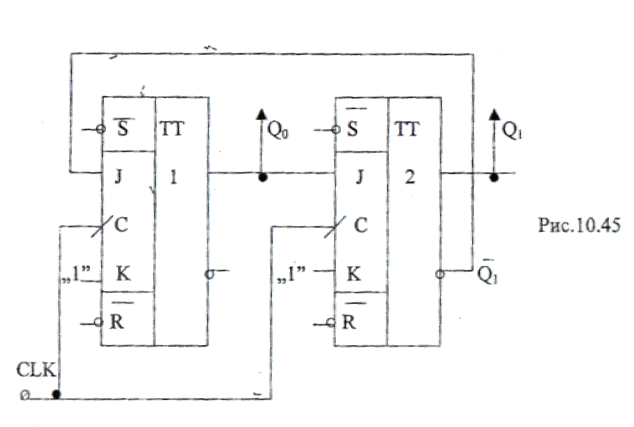

25. Определите модуль счета счетчика, приведенного на рис. 10.45, и постройте временные диаграммы его работы.

26.Сколько триггеров необходимо использовать для постоения двоичного счетчика с модулем счета К=720?

27. Сколько корпусов ИМС двоично-десятичных счетчиков потребуется для построения счетчика с модулем счета К=10 000?

28. Что представляют собой функциональные элементы, на основе которых может быть построен каскадный счетчик?

29. Как реагирует на поступление очередного счетного импульса

• Суммирующий счетчик?

•• Вычитающий счетчик?

••• Реверсивный счетчик?

30. Назовите основные особенности построения счетчиков с групповым (параллельно- последовательным) переносом.

106

31.Каким образом может быть использовано ступенчатое изменение модуля М в интегральных делителях частоты типа К561ИЕ15(К564ИЕ15)? Напоминаем, что значение модуля М указанных ИМС может принимать значения 2;4;5; 8; 10.

32.Известно,что в наиболее упрощенном виде интегральную микросхему делителя частоты К561ИЕ15(К564ИЕ15) можно условно представить в виде двух каскадно соединенных друг с другом счетчиков. Поясните какие функции должны выполнять при этом указанные счетчики и как они должны взаимодействовать друг с другом.

33.Определите диапазон регулирования коэффициента деления частоты Кд в схеме рис. 10.26(a) при к=9. Где к - номер индекса старшего разряда чисел {А} и {В}, сравниваемых в указанной схеме с помощью цифрового компаратора.

34.Выполните определение максимального значения коэффициента деления частоты Кд. мах и его минимального значения Кд.min для схемы рис. 10.27 при n=10. Где n - число двоичных разрядов числа {D}, формируемого на входах предустановки счетчика.

35.Программируемый делитель частоты построен по схеме рис.10.26(б). Определите частоту его выходных сигналов fвых., если переключатель SA закоммутирован в позицию Fq дешифратор состояния счетчика является десятичным дешифратором, а частота входных сигналов равна fвх.=1МГц.

107

2020-08-05

2020-08-05 244

244