Одновибраторы, запускаемые по включению Uп

Многотактный таймер

Однотактный таймер

Классификация

| R | S | Qn+1 |

| Qn | ||

| н/0 |

В исходном состоянии S1 заперт, Cт разряжен, Uвых=0. При подаче на запуск импульса триггер DD перебрасывается в единичное состояние, S1 размыкается, начинается заряд Сt с постоянной времени τ=Ct∙Rt. Как только напряжение на Сt достигает Uоп на выходе DA появляется высокий уровень, который перебрасывает DD в 0-ое состояние, S1 – замыкается и разряжает Сt. Таймер ждет нового запускающего импульса. Длительность формируемого импульса примерно равана 0,5 – 0,7 – 1,1 от τ.

Для аварийного прекращения импульса (к.з.) предназначен вход сброса, который замыкает S1 и разряжает Сt.

Получение Uопор от источника питания с помощью Rд позволяет стабилизировать длительность импульса при изменении Uп в широких пределах.

Недостаток: ограниченное время τ=1мс, Rt=1 Мом.

N – коэффициент пересчета.

– однотактный; - многотактный.

Функциональная схема 1006ВИ1 (555)

В исходном состоянии VT1 открыт, Ct разряжен, Uвых=0. UR=0, т.к. UИ1>UНИ1 (напряжение на инвертирующем входе DA1 больше, чем на неинвертирующем). US также равно 0, т.к. UНИ2<UИ2. DD находится в режиме хранения. При подаче на вход 1 отрицательного импульса (импульса низкого уровня) UИ2 станет меньше UНИ2, US=1, UВЫХ DD=0, UВЫХ 3=1, VT1 закроется, Ct начнет заряжаться через Rt.

По мере достижения UCt напряжения, UНИ2 станет больше UИ2, UR=1, RS-триггер перебросится в ноль, на выходе DD появится 1, который установит ноль на выходе 3 и откроет VT1, через который разрядится Ct. Схема вернулась в исходное состояние.

Для исключения неопределенности длительность входного отрицательного импульса должна быть меньше длительности формируемого сигнала. Если это не соблюдается, сигнал нужно подавать на вход 2 с целью его дифференцирования.

Параметры таймера:

1. диапазон напряжения Uп=4,5 – 16 В.

2. потребляемый ток 3 мА.

3. погрешность формирования временного интервала 0,5-1 %.

4. выходной вытекающий/втекающий ток – 200 мА (по выходу 3)

5. Rt<10 МОм.

Вывод 4 – сброс. При подаче на него напряжение, меньшее 0,4 В, таймер возвращается в исходное состояние, Uвых=0. При Uп>1 В вход не влияет на работу схемы.

Подключая к выводу 5 дополнительные делители напряжения можно изменять порог срабатывания компаратора.

VD предназначен для быстрого возвращения в исходное состояние таймера после выключения напряжения питания.

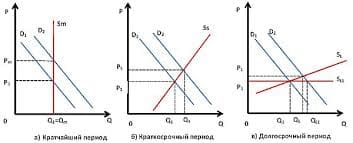

1)

2)

| Схема | t0 | t1 | t2 | Q= | |

| 1,базовая | 1,1(R1+ Rt) Сt | 0,693(R1+ Rt) Сt | 0,693 Сt R1 | ||

| базовая с диодами | 1,2 Сt Rt | 0,76 Сt R1 | 0,76 Сt Rt | ||

| Сt→5 | 0,693(R1+ Rt) Сt | 0,693 Сt R1 | |||

| Сt→5 + диоды | 0,76 Сt Rt | 0,76 Сt R1 |

1)

– время выхода на режим; - длительность импульса; - длительность паузы.

При включении питания Ct разряжен, а значит на неинвертирующем входе DA1 – 0, а на инвертирующем -, следовательно UR=0. На инвертирующем входе DA2 – 0, на неинвертирующем -, следовательно US=1, а значит DD1 находится в единичном состоянии, на его инвертирующем входе ноль, а значит напряжение на выходе 3 имеет высокий уровень, а VT закрыт. Ct начинает заряжаться через Rt и R1. Как только напряжение на нем достигнет величины, компаратор DA1 изменит свое состояние, UR=1 и DD1 перебросится в ноль, что вызовет появление низкого уровня на выходе 3 и отпирание VT1. Теперь Ct начнет разряжаться через R1 до. Тогда перебросятся DA1 и DD1, что вызовет процесс повторного заряда конденсатора Ct.

Недостатки:

1. время выхода на режим больше, чем tИ и tП.

2. tИ > tП

3. При включении питания на выходе сразу высокий уровень, что может вызвать повреждение аппаратуры.

2) Чтобы сделать tП не зависящим от tИ, нужно разделить цепи заряда и разряда с помощью диодов.

Заряд Ct происходит по цепи: +Uп – Rt – VD2 – Ct; разряд: Ct – VD1 – R1 – 7.

3) Лучше когда на выходе низкий уровень. Это достигается:

4)

2014-02-04

2014-02-04 495

495