Аппаратная реализация преобразователя с использованием элементов М2 и ИЛИ.

|

По сравнению с арифметическим алгоритмом аппаратные затраты на реализацию логического алгоритма существенно меньше, а по быстродействию данная КЛС на порядок выше, так как выдает преобразованный код с запаздыванием равным: t =(N-1)tили .

Наиболее распространенные операции отношения A>B,A<B,A=B. Проверка отношений типа равенство или неравенство для сравниваемых кодов А и В может выполняться с использованием параллельных или последовательных алгоритмов. Рассмотрим последовательный алгоритм, который дает наиболее простое решение. Таблица истинности для сравнения одноразрядных кодов может быть записана в виде:

| A1 | B1 | H1 |

0 0 | ||

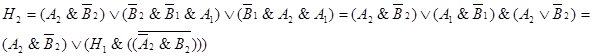

Для двухразрядных кодов: (A2 A1 >B2 B1)

| 10 эквивалент | A2 | A1 | B2 | B1 | H1 |

| A2, A1 | |||||||

| 00 01 11 10 | |||||||

| B2,B1 | |||||||

Распространив подход к определению функции Н2 для проверки отношения A2 A1 >B2 B1 на случай сравнения трехбитных кодов A3A2A1 > B3B2B1, запишем:

|

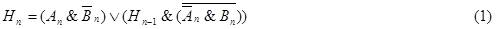

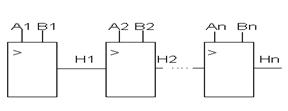

Последовательный алгоритм проверки отношения ‘>’ для сравниваемых n-разрядных кодов может быть записан в виде:

|

Это выражение будет конечным условием формирования отношения:

Ai> Bi i=1,2,….,n

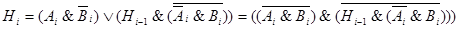

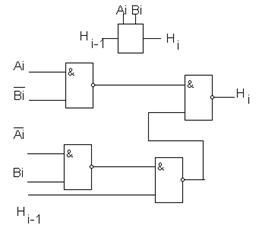

Если в качестве элементной базы для реализации выражения используются элементы И-НЕ, то для сравнения кодов с произвольным числом разрядов i преобразуем выражение к виду:

| |||

|

Если условно принять запаздывание в элементе в элементе сравнения больше чем t>, то суммарное запаздывание может быть вычислено в соответствии со схемной реализацией этого отношения для n – разрядных кодов.

|

tSпос. =Nt>

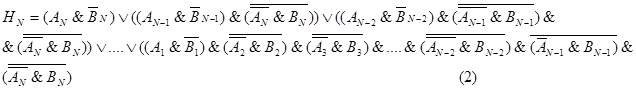

Суммарное запаздывание в схеме последовательного сравнения n – разрядных кодов не позволяет исполнить данную реализацию в быстродействующих КЛС. Альтернативой данному подходу может служить вариант параллельного сравнения кодов, требующий алгоритма вида:

|

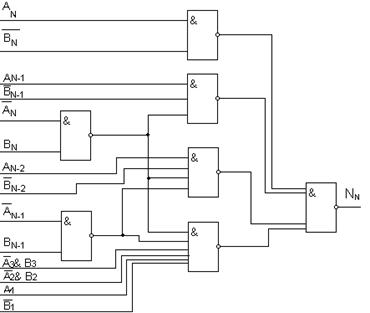

Если сохранить в качестве элементной базы элементы И –НЕ, то выражение может быть реализовано при параллельной подаче на входы схемы N – разрядных сравниваемых кодов.

|

Организация параллельного сравнения N – разрядных кодов повышает быстродействие схемы на величину, зависящую от разрядности сравниваемых кодов с использованием суммарного критерия аппаратных затрат и быстродействия предпочтительно с использованием алгоритма (2), при увеличении разрядности кодов А и В, тот же критерий отдает предпочтение алгоритму (1).

2014-02-02

2014-02-02 900

900