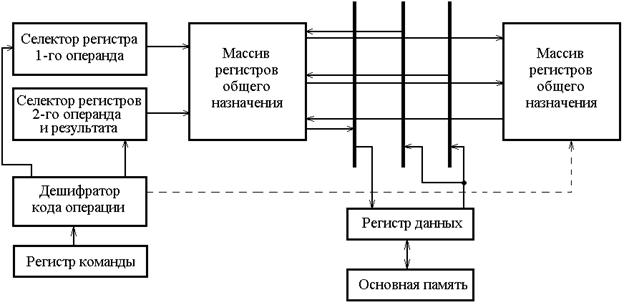

В архитектуре с выделенным доступом к памяти обращение к основной памяти возможно только с помощью двух специальных команд: load и store. Команда load (загрузка) обеспечивает считывание значения из основной памяти и занесение его в регистр процессора (в команде обычно указывается адрес ячейки памяти и номер регистра). Пересылка информации в противоположном направлении производится командой store (сохранение). Операнды во всех командах обработки информации могут находиться только в регистрах процессора (чаще всего в регистрах общего назначения). Результат операции также заносится в регистр.

В архитектуре отсутствуют команды обработки, допускающие прямое обращение к основной памяти. Допускается наличие в архитектуре структуры команд ограниченного числа команд, где операнд является частью кода команды.

Состав и информационные тракты вычислительной машины с выделенным доступом к памяти показаны на рис. 2.52.

Рис. 2.52. Архитектура вычислительной машины с выделенным доступом

к памяти

Архитектура с выделенным доступом к памяти характерна для всех вычислительных машин с RISC-архитектурой. Команды в таких вычислительных машин, как правило, имеют длину 32 бита и трехадресный формат. В качестве примеров вычислительных машин с выделенным доступом к памяти можно отметить HP PA-RISC, IBM RS/6000, SPARC, MIPS R4000, DEC Alpha и т. д. К достоинствам архитектуры следует отнести простоту декодирования и исполнения команды.

2014-02-02

2014-02-02 1222

1222