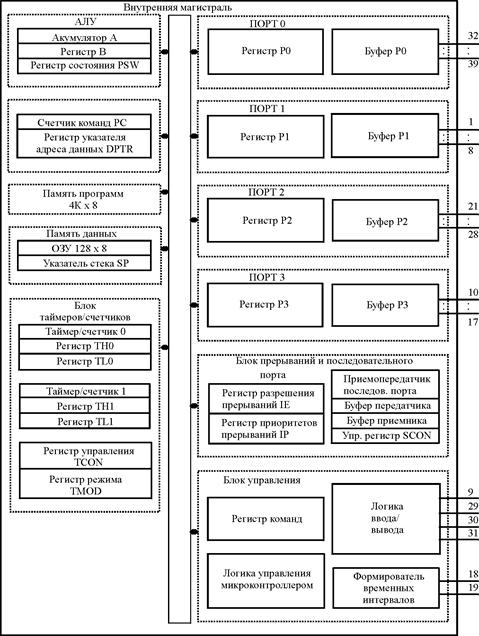

На рис. 3.1 приведена внутренняя структура микроконтроллера 8051АН, исходная для семейства MCS-51. Она включает следующий набор функциональных модулей:

• 8-разрядное АЛУ с аппаратной реализацией операций типа умножение;

• внутренние память программ (4Кбайт) и ОЗУ данных (128 байт);

• четыре универсальных программируемых параллельных 8-разрядных порта ввода-вывода с возможностью реализации определенных альтернативных функций;

• два 16-разрядных программируемых счетчика-таймера;

• дуплексный последовательный порт.

Этот набор аппаратных средств и совокупность реализуемых функций делают микроконтроллеры семейства 8051 эффективным средством сбора предобработки информации и управления объектами. Анализ внутренней структуры микроконтроллеров семейства MCS-51 приводит к выводу, что она имеет полузакрытый характер. Основания к этому следующие:

• набор функций ввода-вывода данных и функций обращения к внешней памяти программ превосходит возможности используемых корпусов по количеству выводов. Причиной этого является значительная роль стоимости корпуса в общей стоимости БИС микроконтроллеров, а следствием - наличие у выводов альтернативных функций и удорожание средств и собственно процесса отладки;

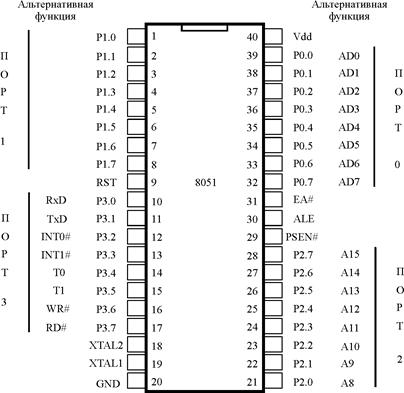

• объединение па кристалле процессора, памяти и блоков ввода-вывода с синхронными режимами работы, таких как таймеры и последовательный порт, приводит к нарушению состояния этих блоков при попытках чтения значений регистров и ячеек памяти процедурами отладки. Переполнение регистров данных этих блоков приводит к установке соответствующих флагов прерываний и может привести к непредусмотренному прерыванию рабочей программы. В наибольшей степени это касается первых микроконтроллеров семейства, которые были созданы с использованием схемотехники динамических элементов. После подачи напряжения питания эти микроконтроллеры невозможно остановить. Внешний вид микросхемы 8051АН, имеющей отечественный аналог К1816ВЕ51, представлен на рис. 3.2. Функции выводов микросхемы 8051 АН следующие.

Port 0. Двунаправленный 8-разрядный параллельный порт ввода-вывода возможностью установки в высокоимпедансное состояние. При работе качестве выходов каждая линия обеспечивает нагрузочную способность равную 8 входам маломощной серии LS TTL. При обращении микроконтроллера к внешней памяти программ или данных порт работает в режиме мультиплексирования младшего байта адреса и 8-разрядной шины данных. При записи в разряд регистра порта Р0 логической «1» соответствующая линия порта переходит в режим высокоимпедансного входа. Для работы в режиме порта ввода-вывода необходимо внешнее подтягивание каждой линии порта к уровню логической «1».

Port 1. Двунаправленный 8-разрядный параллельный порт ввода-вывода. При работе в качестве выходов каждая линия обеспечивает нагрузочную способность, равную 4 входам маломощной серии LS TTL. При записи и разряд регистра порта Р1 логической «1» соответствующая линия порта переходит в режим высокоимпедансного входа со слабым подтягиванием сигнала к уровню логической «1».

Рис. 3.1 - Структура микроконтроллера 8051АН

Рис. 3.2 - Микросхема 8051АН и функции выводов

Port 2. Двунаправленный 8-разрядный параллельный порт ввода-вывода. При работе в качестве выходов каждая линия обеспечивает нагрузочную способность, равную 4 входам маломощной серии LS TTL. При записи в разряд регистра порта Р2 логической «1» соответствующая линия порта переходит в режим высокоимпедансного входа со слабым подтягиванием сигнала к уровню логической «1». При обращении микроконтроллера к внешней памяти программ или данных с использованием 16-разрядного адреса (команды MOVX@DPTR) через порт Р2 выдается старший байт адреса. При обращении микроконтроллера к внешней памяти данных с использованием 8-разрядного адреса (команды MOVX@Ri) на выводы порта Р2 выдается содержимое регистра специальных функций Р2.

Port 3. Двунаправленный 8-разрядный параллельный порт ввода-вывода. При работе в качестве выходов каждая линия обеспечивает нагрузочную способность, равную 4 входам маломощной серии LS TTL. При записи в разряд регистра порта РЗ логической «1» соответствующая линия порта переходит в режим высокоимпедансного входа со слабым подтягиванием сигнала к уровню логической «1». Выводы порта РЗ могут выполнять альтернативные функции, как показано ниже.

Вывод Альтернативная функция

Р3.0. RxD - вход приемника последовательного порта

Р3.1. TxD - выход передатчика последовательного порта

Р3.2. INT0 - вход внешнего прерывания 0

Р3.3. INT1 - вход внешнего прерывания 1

Р3.4. Т0 - внешний вход таймера/счетчика 0

Р3.3. Т1 - внешний вход таймера/счетчика 1

Р3.6. WR# - сигнал разрешения записи во внешнюю память данных

Р3.7. RD# - сигнал разрешения чтения из внешней памяти данных

RST. Вход инициализации (сброса). Высокий уровень на этом входе в течении двух машинных тактов запускает процесс инициализации микроконтроллера.

ALE. Активное значение сигнала на этом выходе разрешает фиксацию младшего байта адреса при обращениях к внешней памяти. У микроконтроллеров типа 8751 с внутренней памятью программ это вывод имеет альтернативную функцию PROG#. При программировании внутренней памяти на него подается стробирующий сигнал.

PSEN#. Активное значение сигнала на этом выходе разрешает чтение из внешней памяти программ.

ЕА#. Сигнал на этом входе переключает источник кода при обращении к младшим 4 Кбайтам памяти программ. При ЕА=0 и диапазоне адресов 0000h..FFFFh микроконтроллер 8051 выполняет цикл обращения к внешней памяти программ, при ЕА=1 обращение по одному из этих адресов приводит к чтению кода из внутренней памяти. У микроконтроллеров типа 8751 с внутренней памятью программ это вывод имеет альтернативную функцию Vpp. При программировании внутренней памяти на него подается напряжение программирования.

XTAL1. Вход инвертирующего усилителя для синхрогенератора.

XTAL2. Выход инвертирующего усилителя для синхрогенератора.

2014-02-03

2014-02-03 1345

1345