Ассоциативная память

Память с выборкой по содержанию является безадресной. Обращение к ней осуществляется по специальной маске, которая содержит поисковый образ. Информация считывается из памяти, если часть ее соответствует поисковому образу, зафиксированному в маске. Например, если в такую память записана информация о людях, содержащая данные о месте жительства (включая город), и необходимо найти сведения о жителях определенного города, то название этого города помещается в маску и дается команда "чтение" - из памяти выбираются все записи, относящиеся к заданному городу.

В микропроцессорах ассоциативные ЗУ используются в составе кэш-памяти для хранения адресной части команд и операндов исполняемой программы. При этом нет необходимости обращаться к ОП за следующей командой или требуемым операндом: достаточно поместить в маску необходимый адрес, и если искомая информация имеется в СОЗУ, то она будет сразу выдана. Обращение к ОП будет необходимо лишь при отсутствии требуемой информации в СОЗУ. За счет такого использования СОЗУ сокращается число обращений к ОП, а это позволяет экономить время.

Кэш-память может быть размещена в кристалле процессора (так называемая "кэш-память I уровня") либо выполнена в виде отдельной микросхемы или модуля, содержащего несколько микросхем (внешняя кэшпамять, или кэш-память II уровня).

Встроенная кэш-память (I уровня) в процессорах Pentium имеет объем 16-32 Кбайт. Внешняя кэш-память (II уровня) имеет объем до 1Гбайта и работает с 64-битными словами.

Основу центрального процессора ПЭВМ составляет микропроцессор (МП) - обрабатывающее устройство, служащее для арифметических и логических преобразований данных, для организации обращения к ОП и ВНУ и для управления ходом вычислительного процесса. В настоящее время существует большое число разновидностей микропроцессоров, различающихся назначением, функциональными возможностями, структурой, исполнением. Наиболее существенными классификационными различиями между ними чаще всего выступают:

- назначение (микропроцессоры для серверов и мощных приложений; МП для персональных компьютеров и т.д.);

- количество разрядов в обрабатываемой информационной единице (8-битные, 16-битные, 32-битные, 64-битные и др.);

- технология изготовления (0.5мкм-технология; 0.35мкм; 0.25мкм; 0.18мкм; 0.13мкм; 0.07мкм, и т.п.).

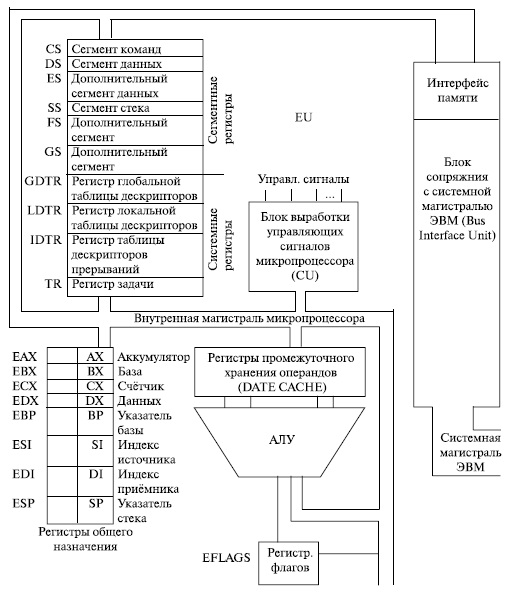

Обобщенная структурная схема 32-разрядного микропроцессора x86 (серии Pentium) приведена на рис.15.3.

Условно микропроцессор можно разделить на три части: исполнительный блок (Execution Unit - EU), устройство сопряжения с системной магистралью (Bus Interface Unit - BIU) и блок управления микропроцессором (Control Unit - CU).

В исполнительном блоке находятся: арифметический блок (кэш данных - DATE CACHE, микросхемы арифметико-логического устройства - АЛУ, регистр флагов), регистры общего назначения (РОН) EAX, EBX, ECX, EDX; общие регистры ESI, EDI, ESP, EBP.

В регистре флагов каждый разряд имеет строго определенное назначение. Обычно разряды регистра флагов устанавливаются аппаратно при выполнении очередной операции в зависимости от получаемого в АЛУ результата. При этом фиксируются такие свойства получаемого результата, как нулевой результат, отрицательное число, переполнение разрядной сетки АЛУ и т.д.

Регистры общего назначения EAX, EBX, ECX, EDX имеют длину по 32 бита. Каждый из них делится на два 16-битных регистра, младший из которых имеет свое имя (что обеспечивает совместимость с 16-разрядными версиями микропроцессоров). Так, в регистре EAX содержится 16-битный регистр AX, в регистре EBX содержится регистр BX, в ECX - регистр CX, в EDX - регистр DX. Каждый из 16-битных регистров, в свою очередь, состоит из двух 8-битных регистров, имеющих свои имена. Например, АХ (аккумулятор) делится на AH и AL, регистр базы (Base Register) - BX, делится на BH и BL. Счетчик (Count Register) CX включает регистры CH и CL. Регистр данных (Data Register) DX содержит регистры DH и DL. Каждый из коротких регистров может использоваться самостоятельно или в составе регистровой пары. Условные названия (аккумулятор, регистр базы, счетчик, регистр данных) не ограничивают применения этих регистров - эти названия говорят о наиболее частом их использовании или об особенности применения того или иного регистра в той или иной команде. Буква "Н" в имени 8-битного регистра означает верхний (или старший) регистр, буква "L" - младший (т.е. младший байт 16-битного регистра или младший однобайтный регистр двухбайтного регистра).

Рис. 15.3. Обобщенная структурная схема 32-разрядного микропроцессора

Эти регистры используются для операций с данными, такими как сравнение, математические операции или запись данных в память. Регистр СХ чаще всего применяется как счетчик циклов.

Общие регистры - ESP, EBP, ESI, EDI также 32-битные, младшая половина которых доступна как регистры S P, B P, SI, DI.

Регистр ESP указывает на адрес вершины стека (адрес, куда будет заноситься следующая переменная командой PUSH).

Регистр ЕВР содержит адрес базы, который может использоваться при работе со стеком.

Регистр ESI - адрес источника, обычно содержит адрес начала блока информации для операций типа "переместить блок", а регистр EDI - адрес приемника (назначения) в этой операции.

Блок управления микропроцессором содержит сегментные регистры, системные регистры и блок выработки управляющих сигналов микропроцессора.

Сегментные регистры CS, DS, ES, FS, GS, SS имеют длину по 16 бит и используются для формирования физических адресов команд и данных в основной памяти.

CS - сегмент кода исполняемой в данный момент программы.

DS - сегмент данных исполняемой программы, т.е. константы, строковые ссылки и т.д.

SS - сегмент стека исполняемой программы.

ES, FS, GS - дополнительные сегменты, которые в некоторых программах могут не использоваться.

Системные регистры GDTR и LDTR являются регистрами глобальной и локальной дескрипторных таблиц. GDTR имеет длину 48 бит, LDTR - 16 бит (точнее, 16 бит - это только "видимая" часть этого регистра).

Регистр IDTR (таблицы дескрипторов прерываний - DTR) имеет длину 48 бит, 32 из которых являются базовым адресом таблицы дескрипторов прерываний (IDT), а 16 - смещением этого адреса (пределом).

Регистр TR является регистром состояния задачи. "Видимая" его часть имеет длину 16 бит и содержит селектор дескриптора. "Скрытая" часть регистра содержит загружаемые автоматически базовый адрес точки входа, предел и атрибуты задачи.

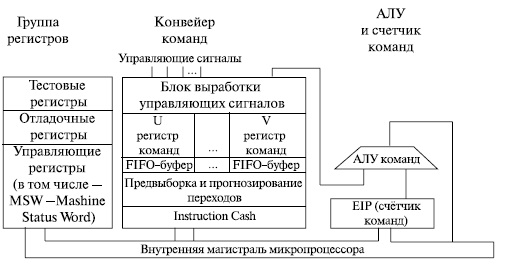

Структурная схема блока выработки управляющих сигналов микропроцессора приведена на рис.15.4.

Основу его составляют счетчик команд, АЛУ, конвейер команд и группа управляющих, отладочных и тестовых регистров.

Регистр EIP является указателем адреса команды (Instruction Pointer), которая будет выбираться в конвейер команд в качестве очередной команды (в отечественной литературе такое устройство называется счетчик команд).

Рис. 15.4. Структурная схема блока выработки управляющих сигналов

Конвейер команд МП хранит несколько команд, что позволяет при выполнении линейных программ совместить подготовку очередной команды с выполнением текущей. Команды в конвейер команд поступают с внутренней магистрали микропроцессора и накапливаются в кэше команд. Блок предвыборки и прогнозирования переходов осуществляет трансляцию команд x86 в RISС-команды, прогнозирует последовательность исполнения команд и направляет полученные последовательности команд в соответствующие ветви конвейера команд (U,V,…). Каждый конвейер команд имеет свой буфер (память магазинного типа FIFO), из которого команды поступают в соответствующий регистр команд для исполнения.

АЛУ команд используется для вычисления физических адресов необходимых для работы микропроцессора команд и данных.

Управляющие регистры - CR0, CR1, CR2, CR3, - имеют длину по 32 бита. Эти регистры устанавливают режим работы процессора (нормальный, защищенный и т.д.), контролируют постраничное распределение памяти, и т.д. Они доступны только для привилегированных программ. Младшая часть регистра CR0 используется как слово состояния машины.

Отладочные регистры - DR0-DR7 - содержат адреса восьми точек прерывания и устанавливают, что должно произойти при достижении программой соответствующей точки прерывания. Эти регистры используются при отладке программы с помощью таких отладочных средств, как debug.exe (для реального режима) или ntsd.exe (для защищенного режима). Тестовые (контрольные) регистры TRj используются для контроля постраничной системы распределения памяти, реализуемой операционной системой.

2014-02-17

2014-02-17 1640

1640