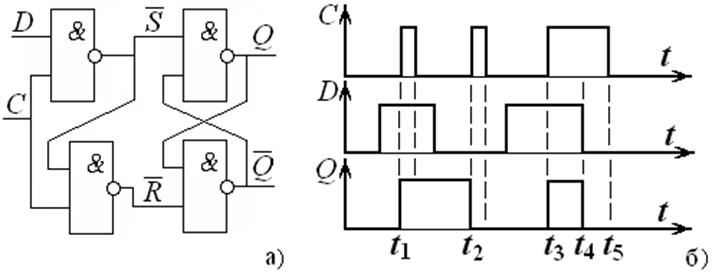

Схема D -триггера (рис. 7) имеет один информационный вход D и тактовый вход C, его таблица истинности табл. 5.

Триггер является простейшей ячейкой памяти и применяется только как синхронный элемент.

Рис. 7 D -триггер на элементах 2И-НЕ:

а – принципиальная схема;

б – временные диаграммы работы

Таблица истинности D -триггера Таблица 5

| № | C | D | Q n +1 |

| X | Q n |

На рисунке 7 представлен синхронный потенциальный D -триггер. Если при наличии тактового сигнала C (интервал t 3 – t 5), происходит изменение входного сигнала D (в момент времени t 4), то это оказывает влияние на состояние выходов.

2014-02-17

2014-02-17 1667

1667