SPI Status Register (SPSR)

Tаблица 8.2

SPI Control Register (SPCR)

| Бит $0D($2D) R/W Нач.знач. | SPCR | ||||||||

| SPIE | SPE | DORD | MSTR | CPOL | CPHA | SPR1 | SPR0 | ||

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | W | ||

Рисунок 8.2 – Регистр управления SPI (SPCR)

Бит 7 - SPIE (SPI Interrupt Enable). Разрешение преывания от SPI. Прерывание возникает при выставлении в «1» флага SPIF регистра SPSR. При этом прерывания должны быть разрешены глобально (бит I регистра SREG).

Бит 6 - SPE (SPI Enable). Разрешение работы SPI. Для разрешения работы бит необходимо выставить в «1».

Бит 5 - DORD (Data Order). Порядок следования данных. При DORD=1 первым передается младший разряд данных, а при DORD=0 – старший.

Бит 4 - MSTR (Master/Slave Select). Выбор режима Master/Slave. При MSTR=1 SPI работает в режиме Master, а при MSTR=0 - в режиме Slave.

Бит 3 - CPOL (Clock Polarity). Полярность тактовых импульсов. При CPOL=0 генерируются импульсы положительной полярности, при отсутствии импульсов на выводе SCK присутствует низкий уровень. При CPOL=1 -отрицательной полярности, при отсутствии импульсов – высокий уровень.

Бит 2 - CPHA (Clock Phase). Фаза тактовых импульсов. При CPHA=0 обработка данных производится по переднему фронту импульсов сигнала SCK (при CPOL=0 – по нарастающему, а для CPOL=1 – по спадающему фронту). При CPHA=1 - по заднему фронту.

Биты 1,0 - SPR1, SPR0 (SPI Clock Rate Select 1 and 0). Задание частоты тактового сигнала SCK в режиме “Master”. В режиме Slave эти биты не задействованы. Значения частоты тактового сигнала SCK приведены в табл.8.2.

Значения частоты тактового сигнала SCK

| SPR1 | SPR2 | Частота сигнала SCK |

| FCLK/4 | ||

| FCLK/16 | ||

| FCLK/64 | ||

| FCLK/128 |

Контроль состояния модуля SPI осуществляется с помощью регистра состояния SPSR (доступен только для чтения), расположенного по адресу $0E ($2E). Формаг этого регистра приведен на рис.8.3.

| Бит $0E($2E) R/W Нач.знач. | SPCR | ||||||||

| SPIF | WCOL | - | - | - | - | - | - | ||

| R | R | R | R | R | R | R | R | ||

Рисунок 8.3 – Регистр состояния SPI (SPSR)

Бит 7 - SPIF (SPI Interrupt Flag). Флаг прерывания от SPI. Устанавливается в «1» по окончании передачи очередного байта, а также при переводе микроконтроллера из режима Master в режим Slave посредством вывода SS (см. раздел 3.3). Флаг сбрасывается аппаратно либо при старте подпрограммы обработки прерывания, либо после чтения регистра состояния SPI с последующим обращением к регистру данных SPDR.

Бит 6 - WCOL (Write Collision Flag). Флаг конфликта записи. Устанавливается в «1» при попытке записи в регистр данных SPDR во время передачи очередного байта. Флаг сбрасывается аппаратно после чтения регистра состояния SPI c последующим обращением к регистру данных SPI.

Биты 5…0 – Зерезервированы, читаются как «0».

| Бит $0F ($2F) R/W Нач.знач. | SPDR | ||||||||

| MSB | - | - | - | - | - | - | LSB | ||

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | ||

Рисунок 8.4 – Регистр ввода – вывода SPI (SPDR)

Передаваемые данные записываются, а принимаемые — считываются из регистра данных SPDR, расположенного но адресу $0F ($2F). Запись в этот регистр инициирует начало передачи, а при его чтении считывается содержимое приемного буфера сдвигового регистра. Поэтому этот регистр можно назвать буфером между регистровым файлом микроконтроллера и сдвиговым регистром модуля SPI.

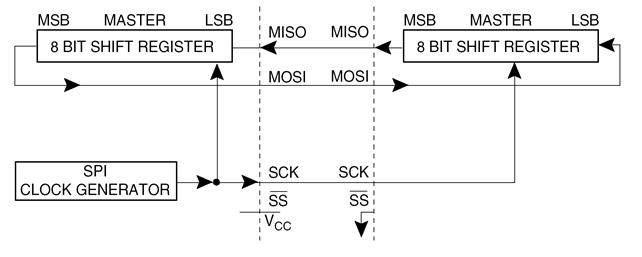

Соединение двух микроконтроллеров (ведущий ведомый) по интерфейсу SPI показано на рис.8.5. Вывод SCK ведущего микроконтроллера является выходом тактового сигнала, а ведомого микроконтроллера — входом.

2014-02-24

2014-02-24 1029

1029