Параллельно-последовательные (универсального типа) регистры

6.1 Параллельно-последовательные регистры сочетают в себе свойства регистров с параллельной записью слова и сдвигающих регистров. Обычно такие регистра содержат общий установочный асинхронный вход сброса всех разрядов в 0.

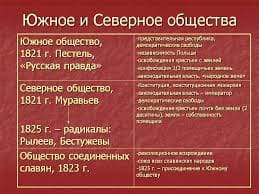

Таблица 1 - Алгоритм работы

| PL | DSR | DSL | S0 | S1 | Режимы |

| Хранение | |||||

| Сдвиг вправо | |||||

| Сдвиг влево | |||||

| Параллельная запись |

Рисунок 8 - Обозначение параллельно-последовательного регистра и таблица его режимов.

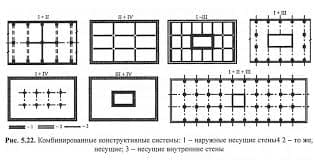

Рисунок 9 - Функциональная схема 2-х разрядов параллельно-последовательного регистра с цепями управления..

В зависимости от кодовой комбинации управляющих сигналов S0 и S1 регистр может использовать любую из 4х микроопераций: хранение, сдвиги влево и вправо, запись параллельного кода. Если S0 = S1=0, то сигнал Y0 дешифратора блокирует прохождение синхроимпульса и регистр хранит записанную информацию. Выходы Y1,Y2,Y3 дешифратора управляют коммутаторами на м/с И-ИЛИ-НЕ и обеспечивает прохождение на вход одного из 3х сигналов. .Выбранный сигнал подается на триггер и определяет режим сдвига слова влево или вправо или запись параллельного кода. Выходы триггеров YLi и YRi соединены внутри регистра с соответствующими входами

.Выбранный сигнал подается на триггер и определяет режим сдвига слова влево или вправо или запись параллельного кода. Выходы триггеров YLi и YRi соединены внутри регистра с соответствующими входами  триггеров.

триггеров.

2014-02-09

2014-02-09 432

432