Архитектура фон Неймана обладает тем недостатком, что она последовательная. Какой бы огромный массив данных ни требовалось обработать, каждый его байт должен будет пройти через МП, даже если над всеми байтами требуется провести одну и ту же операцию. Этот эффект называется узким горлышком фон Неймана.

Для преодоления этого недостатка предлагались и предлагаются архитектуры процессоров, которые называются параллельными. Параллельные процессоры используются в суперкомпьютерах. Возможными вариантами параллельной архитектуры могут служить (по классификации Флинна):

· SISD — один поток команд, один поток данных;

· SIMD — один поток команд, много потоков данных;

· MISD — много потоков команд, один поток данных;

· MIMD — много потоков команд, много потоков данных.

Конвейерная архитектура (Pipelining) была введена в ЦП с целью повышения быстродействия. Обычно для выполнения каждой команды требуется осуществить некоторое количество однотипных операций, например: выборка команды из ОЗУ, дешифровка команды, адресация операнда в ОЗУ, выборка операнда из ОЗУ, выполнение команды, запись результата в ОЗУ. Каждую из этих операций сопоставляют одной ступени конвейера. Например, конвейер МП с архитектурой IA-32 содержит 6 модулей, корые выполняют стадии обработки:

· Модуль шинного интерфейса, ввод/вывод данных.

· Модуль предварительной выборки, считывание инструкции и помещение ее в очередь.

· Модуль декодирования, выборка инструкции из очереди и ее декодирование.

· Модуль выполнения, исполняет последовательность инструкций, полученных от модуля декодирования. операций,

· Модуль сегментации, преобразует логические адреса в линейные адреса и выполняет проверки, связанные с защитой памяти.

· Модуль страничной организации преобразует линейные адреса в физические адреса памяти, выполняет проверки адресов, связанные с защитой страниц памяти, а также ведет список страниц, к которым недавно осуществлялся

Предположим, что каждый этап выполнения команды в процессоре длится ровно 1 машинный такт. На рисунке показана матрица шестиступенчатого выполнения команд в процессоре, не поддерживающем режим конвейерной обработки. Подобный режим выполнения команд был реализован в процессорах фирмы Intel до появления на свет модели Intel486.

Как только завершается этап Э6 выполнения команды К-1, начинается выполнение этапа Э1 команды К-2. При этом для выполнения двух команд К-1 и К-2 требуется 12 машинных тактов. Другими словами, если цикл выполнения команды состоит из к этапов, то для выполнения последовательности из n команд потребуется n x к машинных тактов. Очевидно, что подобный ЦП работает крайне неэффективно, поскольку за 1 машинный такт выполняется только одна шестая часть команды.

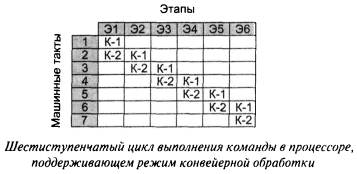

В то же время, если в процессоре поддерживается режим конвейерной обработки, то уже на втором машинном такте процессор может приступить к этапу Э1 выполнения новой команды. При этом предыдущая команда будет находиться на этапе Э2 своего выполнения. Таким образом, конвейерная обработка позволяет совместить выполнение двух машинных команд во времени. Как только процессор переходит к этапу Э2 выполнения команды K1, начинается выполнение этапа Э1 команды К-2. Вследствие этогодля выполнения 2 машинных команд требуется уже не 12, а всего лишь 7 машинных тактов. При полной загрузке конвейера, в текуший момент времени работают все 6 его ступеней.

Факторы, снижающие эффективность конвейера:

· Простой конвейера, когда некоторые ступени не используются (например, адресация и выборка операнда из ОЗУ не нужны, если команда работает с регистрами).

· Ожидание: если следующая команда использует результат предыдущей, то последняя не может начать выполняться до выполнения первой (это преодолевается при использовании внеочередного выполнения команд — out-of-order execution).

· Очистка конвейера при попадании в него команды перехода (эту проблему удаётся сгладить, используя предсказание переходов).

Некоторые современные процессоры имеют более 30 ступеней в конвейере, что увеличивает производительность процессора, однако приводит к большому времени простоя (например, в случае ошибки в предсказании условного перехода). Не существует единого мнения по поводу оптимальной длины конвейера: различные программы могут иметь существенно различные требования.

Процессор с одним конвейером называется скалярным.

2014-02-09

2014-02-09 6423

6423