Генератор импульсов – неотъемлемая часть любой цифровой схемы. Его назначение – создать импульсную последовательность с заданным периодом, длительностью импульсов и амплитудой. Генератор может быть построен на логических элементах НЕ, И-НЕ или ИЛИ-НЕ. Рассмотрим простейшую схему генератора на двух логических элементах И-НЕ. Элементы И-НЕ (а не просто НЕ) выбраны с целью осуществления управлением режимом генерации внешним сигналом (рис. 5.1. 14).

Рис. 5.1 14. Схема генератора импульсов на элементах И-НЕ

При подаче на вход управления уровня логического 0 генератор заторможен, т.е. его работа запрещена. Это объясняется тем, что любой ноль на входе элемента И-НЕ однозначно определяет состояние выхода этого элемента и никакие изменения невозможны. В точке В (рис. 14) схемы уровень логической 1, а в точке D – 0. Если же на вход управления подать уровень логической единицы, то состояние выхода первого элемента (точка В) будет определяться уровнем напряжения в точке А. Напряжение же в точке А определяется процессами заряда и разряда конденсатора С через резистор R. Логический элемент DD1 при этих условиях выполняет функцию НЕ.

Предположим, что напряжение в точке В соответствует уровню логического 0. Тогда в точке D – уровень логической 1. Будем для определенности считать, что напряжение логического 0 равно 0 В, а логической единицы – 3,5 В. Тогда можно рассмотреть упрощенные схемы (без логических элементов), представленные на рис. 15. Если считать, что конденсатор разряжен, то напряжение в начальный момент времени в точке А равно напряжению в точке D (рис. 15а).

Рис. 5.2. 15.1 Эквивалентные схемы генератора в различные моменты

времени и диаграммы напряжений

Это связано с инерционностью конденсатора: его заряд не может измениться мгновенно. Напряжение на конденсаторе определяется известной формулой UC =q / C, где q – заряд конденсатора, С – его емкость. Если заряд изменяется во времени, а так оно и будет по мере заряда конденсатора, то эта формула выглядит так:

При t=0 интеграл равен 0 и UC =0.

Итак, в момент времени t0 = 0 на обоих входах элемента DD1 уровень логической единицы, что и определяет ноль в точке В. С течением времени конденсатор С заряжается через резистор R, напряжение на конденсаторе увеличивается, а на резисторе уменьшается и стремится к уровню логического 0 (см. рис. 15е – моменты времени от t0 до t1). При напряжении переключения элемента (1,4 В) в момент времени t1 (рис. 15б) конденсатор зарядится до (3,5 – 1,4) = 2,1 В.

На рис. 15в отражен тот же момент времени t1 после переключения элемента. Теперь в точке А напряжение отрицательно, что соответствует уровню логического 0. Начинается процесс перезаряда конденсатора (моменты времени t1 - t2 на диаграммах напряжений). К моменту времени t2 конденсатор зарядится до напряжения переключения логического элемента (1,4 В) (рис. 15г), элемент переключится (рис. 15д), а напряжение в точке А равно сумме напряжения в точке D (3,5 В) и напряжения на заряженном конденсаторе (1,4 В). Далее процесс повторяется с той же периодичностью и на выходе генератора (точка D) появится периодическая последовательность импульсов. Период следования импульсов определяется временем заряда и разряда конденсатора С через резистор R и пропорционален RC (T ~ RC). Для схем ТТЛ серии 155 величина сопротивления резистора не должна превышать 1,5 кОм, а емкость конденсатора может варьироваться в широких пределах, обеспечивая период колебаний от десятков секунд до десятых долей микросекунды. Ограничение на величину резистора R связано с тем, что при большем чем 1,5 кОм сопротивлении логический элемент DD1 не будет переключаться из нулевого состояния в единичное и генерация прекратится.

Формирователи импульсов предназначены для создания импульсов в нужный момент времени и заданной заранее длительности. Очень часто возникает задача формирования короткого импульса по фронту или срезу другого сигнала любой длительности. Одна из схем такого формирователя по фронту входного сигнала с диаграммами напряжений представлена на рис.5.2 16. В схеме используется 4 логических элемента И-НЕ, причем первые три выполняют функцию НЕ, так как входы элементов соединены вместе (один вход можно подключить к шине с уровнем логической 1 или оставить свободным). Это сделано для того, чтобы использовать один корпус интегральной микросхемы (например, К155ЛА3), внутри которой имеется 4 логических элемента И-НЕ.

Рис.5.3 16. Схема формирователя импульсов по фронту входного

сигнала и диаграммы напряжений

Анализ этой схемы можно проводить только с помощью диаграмм напряжений с учетом того, что сигнал появляется на выходе логического элемента не мгновенно, а с некоторой задержкой (tз). Если задержки не учитывать и рассматривать только уровни напряжений во всех точках схемы, то при любом логическом уровне на входе на выходе всегда будет логическая 1. Логические элементы DD1, DD2 и DD3 инвертируют сигнал, который появляется на соответствующем выходе с задержкой tз. Это и отражено на диаграммах напряжений для точек В, С и D. На входы элемента DD4 действуют 2 сигнала А и D (на рис. 16 они помечены звездочками). Вспоминая логику элемента И-НЕ (табл. 2), замечаем, что только при одновременном появлении уровней логической 1 на входах А и D, на выходе появится уровень логического 0, а если хотя бы на одном входе – 0, на выходе единица. Из диаграмм видно, что совпадение двух единичных сигналов происходит в моменты времени, связанные с задержкой сигнала, проходящего по трем элементам от точки А до точки D. Сигнал на выходе имеет длительность 3tз. С помощью этой схемы можно не только формировать импульсы по фронту входного сигнала, но и определять время задержки распространения сигнала через логический элемент, измеряя длительность выходного импульса с помощью электронного осциллографа.

Одна из схем формирования импульсов заданной длительности приведена на рис.5.3 17. Эта схема получила название одновибратор или ждущий мультивибратор, На вход схемы подается сигнал произвольной длительности, запускающий процесс формирования выходного импульса, возникающего по фронту входного сигнала, с длительностью, заданной разработчиком. Схема построена на однотипных элементах И-НЕ, хотя только один элемент (DD2) выполняет функцию И-НЕ. Все остальные элементы выполняют функцию НЕ. Прежде чем анализировать эту схему, необходимо выяснить начальные уровни напряжений во всех точках схемы и возможность запуска схемы.

В начальный момент времени (до подачи входного импульса запуска схемы) А = 0, В = 1 (см. диаграммы на рис. 17). Для того, чтобы информация в точке В воспринималась элементом DD2, необходимо в точке F обеспечить уровень логической 1. Это можно достичь, выбирая величину сопротивления резистора R меньше 1,5 кОм.

Рис.5.4 17. Схема одновибратора и диаграммы напряжений

Если это условие выполнено, то в точке D уровень 0, и в точке Е также 0. Конденсатор С разряжен. При подаче на вход схемы запускающего положительного импульса, в точке В появится импульс, инверсный входному. В точке D напряжение скачком увеличится до уровня логической 1. Аналогичный скачок произойдет в точке Е, так как конденсатор не может зарядиться мгновенно. Напряжение в точке F примет значение 0. Теперь на входах элемента DD2 логические нули, и на выходе D будет удерживаться высокий уровень, пока на обоих входах DD2 не установятся уровни 1. Т.е. в точке D будет поддерживаться единица в течение действия на входы элемента DD2 наиболее длинного из двух отрицательных импульсов (помечены звездочками на диаграммах напряжений на рис. 17).

Напряжение в точке Е зависит от процесса заряда конденсатора С через резистор R. По мере заряда конденсатора, напряжение на нем растет, а на резисторе, т.е. в точке Е, уменьшается. Как только это напряжение уменьшится до уровня переключения логического элемента (1,4 В), на выходе DD3 появится уровень 1. Выходной импульс сформирован. Его длительность определяется постоянной времени RC - цепи и пропорциональна произведению R и C, т.е. определяется разработчиком схемы. Повторный запуск схемы возможен только после окончания входного импульса и разряда конденсатора.

5.1. Начертите схему генератора импульсов на логических элементах и объясните его работу с помощью диаграмм напряжений и эквивалентных схем.

5.2. Возможно ли в схеме генератора на рис. 14 использовать другие логические элементы (не И-НЕ). Какие это могут быть элементы?

5.3. Возможно ли и как преобразовать схему генератора, чтобы использовалось 3 логических элемента (вместо двух)?

5.4. Объясните как формируется импульс на выходе схемы рис. 16?

5.5. Проанализируйте схему, в которой вместо элементов И-НЕ (рис. 16) установлены элементы ИЛИ-НЕ.

5.6. Проанализируйте схему, в которой вместо последнего элемента И-НЕ (рис. 16) установлен элемент ИСКЛЮЧАЮЩЕЕ ИЛИ.

5.7. Возможно ли в схеме рис. 16 использовать все элементы ИСКЛЮЧАЮЩЕЕ ИЛИ? Как соединять их входы?

5.8. Начертите схему формирователя импульсов заданной длительности и расставьте логические уровни на всех входах и выходах элементов до подачи импульса запуска.

5.9. Каковы условия работоспособности схемы на рис. 17?

5.10. Начертите диаграммы напряжений для формирователя импульсов (рис. 17) при подаче на вход двух коротких импульсов с промежутком между ними меньше длительности выходного сигнала, получаемого при одном запускающем импульсе.

Лекция 6. Регистры

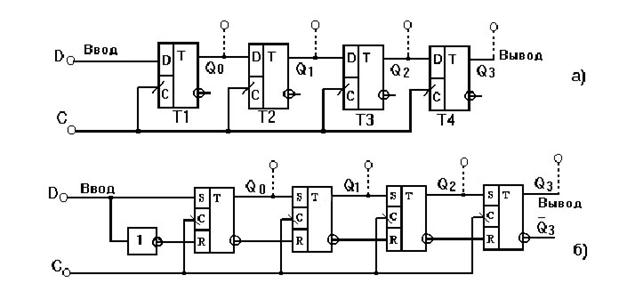

Несколько триггеров можно объединить в регистр - узел для хранения чисел с двоичным представлением цифр разрядов. Основными видами регистров являются параллельные и последовательные (сдвигающие).

В параллельном регистре на тактируемых D-триггерах рисунок 1 код запоминаемого числа подается на информационные входы всех триггеров и записывается в регистр с приходом тактового импульса. Выходная информация изменяется с подачей нового входного слова и приходом следующего синхроимпульса. Такие регистры используют в системах оперативной памяти. Число триггеров в них равно максимальной разрядности хранимых слов.

Рисунок 6. 1

Схема последовательного регистра и временная диаграмма, иллюстрирующая его работу, приведены на рисунке 2. По приходу тактового импульса С первый триггер записывает код X (0 или 1), находящийся в этот момент на его входе D, а каждый следующий триггер переключается в состояние, в которой до этого находился предыдущий. Так происходит потому, что записываемый сигнал проходит со входа D триггера к выходу Q с задержкой, большей длительности фронта тактового импульса (в течение которого происходит запись). Каждый тактовый импульс последовательно сдвигает код числа в регистре на один разряд. Поэтому для записи N-разрядного кода требуется N тактов. На диаграмме видно, что четырёх разрядное число 1011 было записано в соответствующие разряды регистра (1-Q4, 0-Q2, 1-Q2, 1-Q1) после прихода четвёртого тактового импульса. До прихода следующего тактового импульса это число хранится в регистре в виде параллельного кода на выходах Q4-Q1. Если необходимо получить последовательную информацию в последовательном коде, то её снимают с выхода Q4 в момент прихода следующих четырёх импульсов такой режим называется режимом последовательного считывания.

Очень удобны универсальные регистры, позволяющие производить как последовательную, так и параллельную запись и считывание. Такие регистры можно использовать в качестве преобразователя параллельного кода в последовательный и обратно. Например микросхема К155ИР1 - четырёх разрядный универсальный сдвиговый регистр рисунок 3. Регистр работает в режиме сдвига по тактовым импульсам, поступающим на вход С1, если на входе имеется напряжение низкого уровня. Вход V1 служит для ввода информации в первый разряд в этом режиме. Если же на входе V2 напряжение высокого уровня, то регистр производит параллельную запись информации со входов D1-D4 по импульсам синхронизации, поступающим на вход С2.

Рисунок 6.2 2

Рисунок 6.3

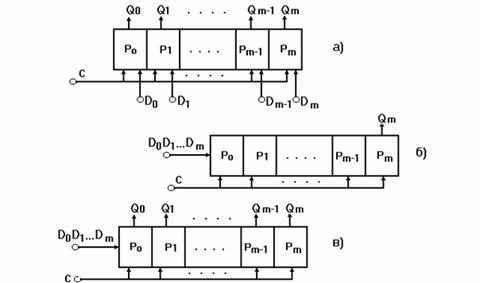

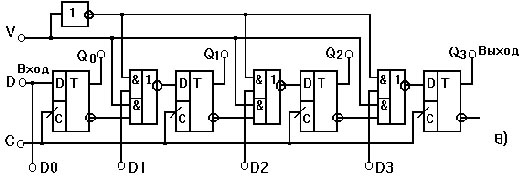

более распространенным узлом цифровой техники и устройств автоматики являются регистры. Регистры строятся на базе синхронных одно- и двухступенчатых RS и D-триггеров. Регистры могут быть реализованы также на базе JK -триггеров. По способу приема и выдачи информации регистры делятся на следующие группы: с параллельным приемом и выдачей (рис. 3.25, а); с последовательным приемом и выдачей); с последовательным приемом и параллельной выдачей (рис. 3.25, в); с параллельным приемом и последовательной выдачей (рис.6.2 3.25, г); комбинированные, с различными способами приема и выдачи (рис.6.2 3.25, д) и реверсивные.

Регистры хранения (пямяти). Регистры с параллельным приемом и выдачей информации служат для хранения информации и называются регистрами памяти или хранения. Изменение хранящейся информации в регистре памяти (запись новой информации) осуществляется после установки на входах D0... Dm новой цифровой комбинации (информации) при поступлении определен ного уровня или фронта синхросигнала (синхроимпульса) С на вход “С” регистра. Количество разрядов записываемой цифровой информации определяется разрядностью регистра, а разрядность регистра, в свою очередь, определяется количеством триггеров, образующих этот регистр. В качестве разрядных триггеров регистра памяти используются синхронизируемые уровнем или фронтом триггеры. -

Рис 6.4

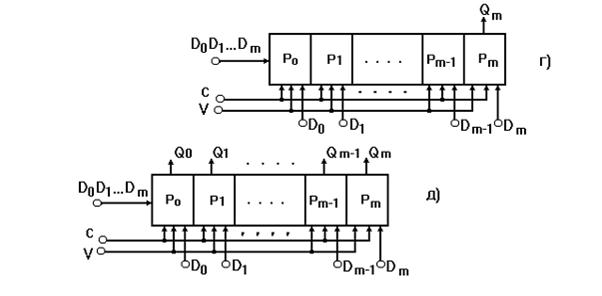

Регистры памяти могут быть реализованы на D-триггерах, если информация поступает на входы регистра в виде однофазных сигналов и на RS-триггерах, если информация поступает в виде парафазных сигналов. В некоторых случаях регистры могут иметь вход для установки выходов в состояние “0”. Этот асинхронный вход называют входом R “сброса” триггеров регистра. На рис.6.5 3.26 приведены схемы четырехразрядных регистров памяти на D- и RS-триггерах, синхронизируемых уровнем и фронтом синхроимпульсов (обычно четыре триггера объединены в одном корпусе ИМС).

а) б) в)

Рис. 6.5. 3.26. Регистры хранения, на D – триггерах, синхронизируемых уровнем синроимпульса (а), фронтом (б) и на RS – триггерах, синхронизируемых фронтом (в)

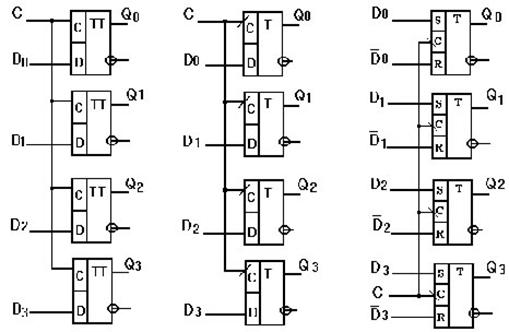

Регистры сдвига. Регистры с последовательным приемом или выдачей информации называются сдвиговыми регистрами или регистрами сдвига. Регистры сдвига могут выполнять функции хранения и преобразования информации. Они могут быть использованы для построения умножителей и делителей чисел двоичной системы счисления, т.к. сдвиг двоичного числа влево на один разряд соответствует умножению его на два, а сдвиг вправо - делению на два. Регистры сдвига широко используются для выполнения различных временных преобразований цифровой информации: последовательное накопление последовательной цифровой информации с последующей одновременной выдачей (преобразование последовательной цифровой информации в параллельный код) или одновременный прием (параллельный прием) информации с последующей последовательной выдачей (преобразование параллельного кода в последовательный). Регистры сдвига могут служить также в качестве элементов задержки сигнала, представленного в цифровой форме. Действительно, регистры с последовательным приемом (вводом) и выводом осуществляют задержку передачи информации на m+1 тактов (m+1 - число разрядов регистра) машинного времени. Регистры сдвига обычно реализуются на D-триггерах (рис. 3.27, а) или на RS-триггерах (рис. 3.27, б), где для ввода информации в первый разряд включается инвертор (первый разряд представляет собой D-триггер). Следует отметить, что все регистры сдвига строятся на базе двухступенчатых триггеров или синхронизируемых фронтом синхроимпульса. Разрядность регистров сдвига, как и у регистров хранения, определяется количеством триггеров, входящих в их состав. На рис. 3.27 приведены схемы четырехразрядных регистров сдвига, реализованных на D- и RS-триггерах, а временные диаграммы, поясняющие работу регистра сдвига, приведены на рис. 3.28.

Вывод параллельной информации из регистра сдвига (см. рис. 3.27, в) осуществляется при подключении всех триггеров регистра к отдельным выводам (на рис. 3.27, а и б эти выводы показаны штриховыми линиями). Как было сказано выше, регистры сдвига синхронизируются фронтом тактирующих импульсов, т.е. запись новой информации в триггеры регистра происходит в течение очень короткого времени - за время длительности фронта синхроимпульса, вернее в момент поступления соответствующего фронта синхроимпульса. Обычно, это “время” значительно меньше времени распространения сигнала, т.е. времени переключения триггера регистра в новое состояние. Работу регистра сдвига рассмотрим на примере схемы, приведенной на рис. 3.27, а.

Можно предположить, что в начале все триггеры регистра находятся в состоянии логического нуля, т.е. Q0=0, Q1=0, Q2=0, Q3=0. Если на входе D-триггера Т1 имеет место логический 0, то поступление синхроимпульсов на входы “С” триггеров не меняет их состояния.

Как следует из рис. 3.27, синхроимпульсы поступают на соответствующие входы всех триггеров регистра одновременно и записывают в них то, что имеет место на их информационных входах. На информационных входах триггеров Т2, Т3, Т4 - уровни логического “0”, т.к. информационные входы последующих триггеров соединены с выходами предыдущих триггеров, находящихся в состоянии логического “0”, а на вход “D” первого триггера, по условию примера, подается “0” из внешнего источника информации. При подаче на вход “D” первого триггера “1”, с приходом первого синхроимпульса, в этот триггер запишется “1”, а в остальные триггеры - “0”, т.к. к моменту поступления фронта синхроимпульса на выходе триггера Т1 “ещё” присутствовал логический “0”. Таким образом, в триггер Т1 записывается та информация (тот бит), которая была на его входе “D” в момент поступления фронта синхроимпульса и т.д.

При поступлении второго синхроимпульса логическая “1”, с выхода первого триггера, запишется во второй триггер, и в результате происходит сдвиг первоначально записанной “1” с триггера Т1 в триггер Т2, из триггера Т2 в триггер Т3 и т.д. (рис. 3.28). Таким образом, производится последовательный сдвиг поступающей на вход регистра информации (в последовательном коде) на один разряд вправо в каждом такте синхроимпульсов.

После поступления m синхроимпульсов (на рис. 3.27 и рис. 3.28 m=4) регистр оказывается полностью заполненным разрядами числа, вводимого через последовательный ввод “D”. В течение следующих четырех синхроимпульсов производится последовательный поразрядный вывод из регистра записанного числа, после чего регистр оказывается полностью очищенным (регистр окажется полностью очищенным только при условии подачи на его вход уровня “0” в режиме вывода записанного числа).

Рис. 6.6. 3.27. Регистры сдвига на D – триггерах а), RS – триггерах б) и комбинированный регистр на D - триггерах

Вопросы по теме

1. Параллельный регистр

2. последовательный регистр

3. хранение данных в регистрах

4. регистры сдвига

5. комбинированный регистр сдвига

2014-02-09

2014-02-09 9277

9277