Блок выполнения команд

Блок выполнения команд обеспечивает параллельное и независимое выполнение 6 команд и содержит следующие компоненты:

· кэш-память данных L1;

· файл регистров;

· конвейер выполнения команд;

· узлы выполнения команд для различных типов данных.

Кэш-память данных L1 объемом 16Кбайт поддерживает до четырех одновременных обращений к данным, хранящимся в этой памяти (два чтения и две записи). В этой кэш-памяти могут храниться только данные целого типа.

Управляемый узлом RSE файл регистров хранит доступные отдельной процедуре регистры. При вызове процедур нет необходимости, как при использовании процедур в IA-32, сохранять регистры вызывающей процедуры. Процедура при вызове получает необходимый ей набор регистров (до 96 регистров) из стека регистров в виде кадра (параметры кадра сохраняются в регистре CFM) и после завершения процедуры регистры возвращаются в стек.

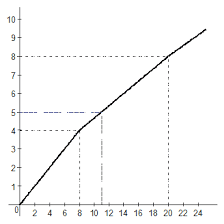

Конвейер (pipeline) выполняет параллельное выполнение шести команд, каждая из которых проходит оставшиеся 6 этапов выполнения (первые два этапа выполняются в блоке загрузки и упреждающей загрузки команд и рассмотрены выше).

На этапе 3 выполняется диспетчеризация команд по конвейерам и, кроме того, назначается узел, который будет выполнять эту команду. Если из-за каких то ограничений команда не может быть выполнена, она временно посылается в буфер команд.

На этапе 4 команда дешифруется, и логические регистры команды преобразуются в физические адреса (аналогично тому, как это делается на этапах 5 и 6 в конвейере процессоров Pentium IV).

На этапе 5 операнды команды загружаются на тот узел, который будет выполнять данную команду, а на этапе 6 команда выполняется назначенным ей узлом выполнения.

На этапе 7 производится проверка на возможные исключения и выявляется ситуация неправильного предсказания перехода.

На этапе 8 результаты выполнения команды записываются в файлы регистров и команда покидает конвейер.

Блок выполнения содержит следующие узлы выполнения команд для наборов команд IA-64 и IA-32:

· 6 узлов выполнения мультимедийных команд;

· 6 узлов выполнения команд обработки данных целого типа;

· 2 узла выполнения команд обработки данных с плавающей точкой;

· 3 узла обработки переходов;

· 4 узла загрузки и сохранения.

Подсистема памяти содержит следующие компоненты:

· кэш-память L2;

· кэш-память L3;

· программируемый контроллер прерываний;

· усовершенствованную таблицу адресов загрузки (ALAT);

· блок сопряжения с системной шиной.

Кэш-память L2 объемом 256 Кбайт является интегрированной памятью, т.е. хранит и команды и данные. Она поддерживает до четырех одновременных запросов одновременно к своему содержимому и имеет пропускную способность 64 Гбайта/с. Обращения к кэш-памяти L2 выполняется в том случае, если данные или команды не были найдены в кэш-памяти L1 (данных и команд). Кроме того, в этой кэш-памяти хранятся и целые данные, и данные с плавающей точкой (в кэш-памяти данных L1 хранятся только целые данные).

Интегрированная кэш-память L3 объемом от 1,5 до 6 Мбайт поддерживает только один запрос к своему содержимому, т.е. если во время обработки запроса поступает другой запрос, он дожидается окончания обработки предыдущего запроса. Скорость обмена данными с кэш-память L1 или L2 составляет 64 Гбайта за один такт.

При проектировании архитектуры IA-64 была разработана новая схема обработки прерываний, реализованная в программируемом контроллере прерываний и в BIOS. Модуль BIOS только генерирует прерывания и направляет их в процессор. В отличие от предыдущих моделей процессоров, сигналы прерывания поступают в процессор не по отдельным каналам, а по системной шине (вместе с данными и командами). Контроллер обрабатывает прерывания, поступающие к нему от модуля BIOS, от других процессоров (в многопроцессорном компьютере), а также те прерывания, которые могут возникать в самом процессоре (например, при мониторинге производительности).

Для принятия решения о предполагаемых загрузках данных в архитектуре IA-64 используется усовершенствованная таблица адресов загрузки – ALAT (Advanced Load Address Table), представляющая собой кэш-память. Таблица содержит сведения о предполагаемых загрузках данных и соответствующих им сохранениях данных и может выполнить две загрузки и два сохранения данных за один такт.

Оперативная память доступна процессору через 128-разрядную системную шину с помощью блока сопряжения с системной шиной.

2014-02-10

2014-02-10 585

585