Компромиссы миниатюризации

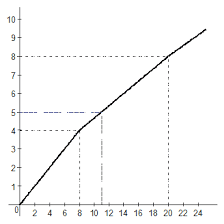

В процессе проектирования типичной является ситуация, когда улучшение одних функциональных характеристик (например, быстродействия) негативно сказывается на надежности приборов и некоторых других функциональных характеристиках. Например, высокое быстродействие требует высоких значений электрических полей, что приводит к ряду нежелательных эффектов.

Во-первых, растут токи утечки (через затворный изолятор и между стоком и истоком, стоком и подложкой). Во-вторых, возникает эффект износа подзатворного окисла, что приводит к резкому увеличению токов утечек через подзатворный изолятор и к его пробою. В-третьих, высокие электрические поля приводят к снижению времени жизни приборов из-за деградации горячими носителями, возникающими в канале в сильном поле между стоком и истоком.

Другая проблема состоит в дилемме − высокое быстродействие или низкое динамическое энергопотребление. Для того чтобы уменьшить время переключения (т.е. увеличить тактовую частоту и быстродействие), нужно увеличить максимальные токи и, соответственно, энергопотребление.

Сформулированы два вида ограничений при масштабировании МОПТ. Первый вид ограничений связан с необходимостью снижения токов утечки и объясняется следующими причинами: снижением порогового напряжения при уменьшении длины канала, смыканием ОПЗ областей стока и истока в объеме подложки, туннелированием носителей между областями стока и подложки при высокой напряженности электрического поля в области перекрытия стока затвором (GIDL - эффект), лавинным пробоем р-п перехода сток- подложка.

Второй вид ограничения масштабирования вызван необходимостью обеспечения надежного функционирования ИС в течение заданного срока службы приборов. Он связан с воздействием горячих носителей и зависимым от времени пробоем подзатворного диэлектрика.

Пределы масштабирования диктуются постоянством фундаментальных и технологических характеристик материала, большинство из которых не поддаются масштабированию. Это, например:

ширина запрещенной зоны кремния (ограничивает снизу пороговое напряжение, ширину обедненной области);

эффективная масса носителей (ограничивает сверху подвижность, скорость насыщения и быстродействие);

внутренние характеристики материалов − например, поле в подзатворном окисле SiO2 не может превышать максимальное напряжение пробоя окисла (~ 107 В/см).

Другой причиной ограничения масштабирования являются некоторые фундаментальные законы, лежащие в основе работы прибора. Например, подпороговые токи утечки между стоком и истоком определяются больцмановской статистикой надбарьерного перехода носителей между стоком и истоком и, вообще говоря, не зависят от геометрических размеров приборов. Паразитные туннельные токи при масштабировании даже возрастают (лекция 7).

Кроме того, при малых размерах начинает работать геометрический фактор, связанный с ухудшением электростатического контроля заряда в канале зарядом на затворе. Это является следствием нарушения планарности и проявлением трехмерности уравнения Пуассона, что приводит к появлению паразитных короткоканальных эффектов (лекция 5).

Возрастание последовательных паразитных сопротивлений истоков/стоков (S/D) – уменьшение максимального тока. Возможное решение состоит в использовании металлических контактов в качестве стоков и истоков (лекция 5).

Обеднение затвора приводит к падению потенциала на затворе и выражается в уменьшении эффективной затворной емкости. Возможное решение состоит в использовании металлических затворов вместо поликремниевых (лекция 3).

Уменьшение размеров и использование нетрадиционных изоляторов уменьшает подвижность. Возможное решение состоит в использовании для увеличения подвижности Si/Ge сплавов и слоев напряженного кремния (лекция 4).

Литература:

1. Зебрев Г.И. Физические основы кремниевой наноэлектрники, М.: БИНОМ, 2011, с. 5-8, 30-53.

2. Парменов Ю.А. Элементы твердотельной наноэлектроники. Учебное пособие. М.: МИЭТ, 2011, гл. 1.

3. Балашов А.Г., Крупкина Т.Ю., Лосев В.В., Старосельский В.И. Наноэлектронные устройства и их модели. Учебное пособие. М.: МИЭТ, 2011, с. 16-29.

4. Красников Г.Я. Конструктивно-технологические особенности субмикронных МОП-транзисторов, Москва: Техносфера, 2011.

5. Semiconductor Industry Association (SIA), The International Technology Roadmap for Semiconductors, 2013, Available online at www.itrs.net.

6. R.H. Dennard, F.H. Gaensslen, V.L. Rideout, E. Bassous, and A.R. LeBlanc, “Design of Ion-Implanted MOSFET's with Very Small Physical Dimensions,” IEEE Journal of Solid-State Circuits, Oct. 1974.

7. Skotnicki T., Hutchby J.A., Tsu-Jae King, Boeuf F. The end of CMOS scaling, IEEE Circuits and Devices Magazine, 2005, №1-2, pp.16-26.

8. Frank D.J., Dennard R.H., Nowak E. at al. Device Scaling Limits of Si MOSFETs and Their Application Dependencies, Proceedings of the IEEE, 2001, v.89, №3, pp.259-288.

9. Critchlow D.L. MOSFET Scaling—The Driver of VLSI Technology. Proceedings of the IEEE, 1999, v.87, №4, pp.659-667.

10. Wong P., Frank D.J., Solomon P.M. at al, Nanoscale CMOS. Proceedings of the IEEE, 1999, v.87, №4, pp.537-570.

11. Chenming Hu. Future CMOS Scaling and Reliability. Proceedings of the IEEE, 1993, v.81, №5, pp.682-689.

12. W. Haensch,E. J. Nowak,R. H. Dennard,P. M. Solomon,A. Bryant,O. H.Dokumaci,A. Kumar,X. Wang,J. B. Johnson,M. V. Fischetti Silicon CMOS devices beyond scaling, IBM J. RES. & DEV. VOL. 50 NO. 4/5 JULY/SEPTEMBER 2006, pp.339-361.

13. H.-S. P. Wong Beyond the conventional transistor, IBM J. RES. & DEV. VOL. 46 NO. 2/3 MARCH/MAY 2002, pp. 133-168

14. Nowak E. J. Maintaining the benefits of CMOS scaling when scaling

bogs down, IBM J. RES. & DEV. VOL. 46 NO. 2/3 MARCH/MAY 2002, pp. 169-180.

15. Y. Taur, Y.-J.MII, D. J. Frank, H.-S. Wong, D. A. Buchanan,S. J. Wind, S. A. Rishton, G. A. Sai-Halasz, E. J. Nowak CMOS scaling into the 21-st century: 0.1  m and beyond, IBM J. RES. DEVELOP. VOL. 39 NO. 112 JANUARYiMARCH 1995, pp. 245-260.

m and beyond, IBM J. RES. DEVELOP. VOL. 39 NO. 112 JANUARYiMARCH 1995, pp. 245-260.

16. Mark Horowitz, Elad Alon, Dinesh Patil, Stanford University, Samuel Naffziger, Rajesh Kumar, Intel, Kerry Bernstein, IBM Scaling, Power, and the Future of CMOS, pp. 1-7, https://www-vlsi.stanford.edu/papers/mh_iedm_05.pdf

17. Liu T.-J.K. and Chang L. Transistor Scaling to the Limit, in «Into the Nano Era: Moore’s Law Beyond Planar Silicon CMOS», Ed. H. R. Huff, Springer, 2009, pp.191-223.

18. Marc Van Rossum MOS Device and Interconnects Scaling Physics, in «Advanced Nanoscale ULSI Interconnects: 15 Fundamentals and Applications», Y. Shacham-Diamand et al. (eds.), Springer Science+Business Media, pp. 15-38.

2014-02-10

2014-02-10 982

982