Как было сказано ранее микроконтроллеры AVR представляют собой восьми разрядные RISC-микроконтроллеры с Гарвардской архитектурой и пониженным энергопотреблением. Набор команд, ограниченность которого свойственна RISC-архитектурам тем не менее необычно широк (120 команд), однако при этом сохранено основное преимущество RISC-архитектур повышенное быстродействие и сокращенное число операций обмена с памятью программ. Почти все команды размещаются в одной ячейке программной памяти и выполняются за один такт синхросигнала.Доступ к памяти данных и памяти программ осуществляется по разным шинам (по собственным шинам этих модулей), поэтому можно не только сделать различными разрядности этих шин, но и реализовать параллельное выполнение текущей команды и выборку и дешифрацию следующей.

На рис. 2.6 представлена структурная схема микроконтроллера АТ90S8515. Многие блоки по назначению аналогичны рассмотренным ранее блокам микроконтроллера и имеют такое же назначение. В памяти ЭСППЗУ (EEPROM) хранятся редко изменяемые данные (калибровочные константы и т. п.), Указатель стека используется для организации стека в некоторой области памяти Аппаратного Стека (SRAM). Микроконтроллер имеет 32 программно доступных регистра общего назначения (РОН), которые объединены в регистровый файл. В отличие от ранее

рассмотренного микроконтроллера здесь АЛУ способно выполнять операции над содержимым любой пары РОН, т. е. все регистры непосредственно доступны для АЛУ и регистр – аккумулятор не требуется. Регистр состояния аналогичен рассмотренному ранее регистру PSW и выполняет те же функции.

Структура портов ввода – вывода немного отличается от предыдущего микроконтроллера.Порт представляет собою набор из восьми линий. Каждая из восьми линий любого порта конфигурируется как входная или выходная индивидуально с помощью управляющего слова, загружаемого в регистр направления передачи. Каждый бит этого слова задает конфигурацию своей линии. Вводимые или выводимые данные поступают в регистр данных. Входные и выходные сигналы проходят через буферные каскады (драйверы).

Последовательный SPI (Serial Peripheral Interface) периферийный канал применяется как для программирования микроконтроллера в последовательном режиме, так и для обмена данными с периферийными устройствами или между микроконтроллерами, если они работают в системе. Протокол обмена для SPI предусматривает работу в режиме либо ведущего (master), либо ведомого (slave).

Асинхронный последовательный интерфейс между микроконтроллером и внешними устройствами обеспечивается рассмотренным ранее блоком UART.

Кроме этого в рассматриваемом микроконтроллере имеется аналоговый компаратор напряжения, подключенный к двум специально выделеным линиям порта В. Компаратор позволяет реализовывать ряд достаточно необходимых функций,

например, служить формирователем при измерении длительности или частоты следования импульсов входного сигнала, служить в качестве элемента простейшего АЦП с обратным интегрированием и т. п.

Рис. 2.6. Структурная схема микроконтроллера AVR

Организация памяти и функционирование микроконтроллера AVR.

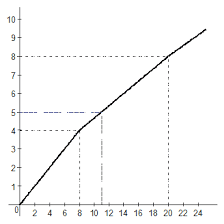

Согласно Гарвардской архитектуре, адресные пространства (АП) для памяти программ и памяти данных разделены. Память данных организована линейно и имеет два адресных пространства. В первом находятся адреса регистровой памяти и адреса статического ЗУ (SRAM). Во втором размещены адреса энергонезависимой

репрограммируемой памяти (EEPROM). Кроме того, возможно подключение к микроконтроллеру внешнего ОЗУ, для которого шины адреса и мультитиплексируемая шина адресов/данных организуется с помощью портов ввода/вывода РА и РС. Линии этих портов формируют 16-разрядные адреса для работы с внешней памятью больших объемов.

Распределение адресного пространства иллюстрируется рис. 2.7.

В регистровой области памяти размещены адреса регистров общего назначения РОН (32 адреса) и регистров ввода/вывода РВВ (64 адреса для адресации 64 байтов памяти). Соответственно общая емкость регистровой памяти составляет 96 байтов. Для адресов статической памяти отведены следующие 512 адресов. Подключение внешнего ОЗУ, как уже отмечалось, может довести емкость до 64 Кбайт. Обращение к внешнему ОЗУ увеличивает время выполнения команды на 1-2 такта для каждого обрабатываемого байта.

В пространстве РВВ размещаются операнды, служебные регистры микроконтроллера и регистры, относящиеся к внешним устройствам. В их числе 12 регистров для работы с портами ввода/вывода (для каждого порта предусмотрены регистр данных, регистр направления данных и регистр выводов. Имеется также регистр – указатель стека.

Энергонезависимая память EEPROM, рассчитана на хранение редко изменяемых данных и имеет длительные операции записи, отличающиеся особым алгоритмом. Доступ к ней производится посредством трех регистров РВВ.

Программы, хранятся во флэш-памяти, а ее разрядность соответствует формату команд и составляет два байта.

Повышению производительности микроконтроллера способствует выполнение почти всех команд за один такт. Такая возможность – следствие конвейерной обработки

информации и непосредственного подключения АЛУ ко всем РОН. В нормальном режиме работы конвейера параллельно выполнению текущей команды происходит выборка и декодирование следующей. При нарушении последовательного

следования команд, например при появлении команды условного перехода, в работе конвейера возникает разрыв и время выполнения команды увеличивается до 2-4 тактов.

Начало выполнения программы инициируется сигналом сброса, после которого микроконтроллер обращается к стартовому адресу программы.

Рис. 2.6. Адресные пространства микроконтроллера AVR

В ходе выполнения программы микроконтроллер выполняет команду за командой, пока не дойдет до команды останова. Большая часть микропрограмм построена так, что определенный набор микрокоманд выполняется циклически, т. е. необходимость в команде останова отпадает.

Все множество команд, выполняемых микроконтроллером, можно разбить на следующие группы:

● команды пересылки данных;

● команды арифметических сдвигов;

● команды логических операций;

● команды операций с битами;

● команды передачи управления;

● команды управления системой.

Сопоставляя перечисленные группы команд с рассмотренными в предыдущей главе для CISC процессоров, можно отметить их большое сходство. Специфичная группа команд операций с битами содержит команды установки и сброса заданного разряда в регистре РОН или РВВ. Для удобства программирования задействованным разрядам регистров РВВ присваиваются символические имена, определение которых дается в специальном файле, подключаемом вначале программы.

2014-02-13

2014-02-13 3549

3549