Архитектура микроконтроллеров

Понимание архитектуры микроконтроллеров является ключевым при изучении языков программирования типа ассемблер. Структура ассемблера, формат его команд, адресация операндов и т. д. полностью определяются архитектурой. Целью изучения архитектуры является:

· выявление набора доступных для программирования регистров, их функционального назначения и структуры;

· понимание организации оперативной памяти и порядка ее использования;

· знакомство с типами данных;

· изучение формата машинных команд;

· выяснение организации обработки прерываний.

·

Архитектура семейства MCS-51 в значительной мере предопределяется ее назначением - построение компактных и дешевых цифровых устройств. Все функции МК реализуются с помощью единственной микросхемы. В состав семейства MCS-51 входит целый ряд микросхем от самых простых микроконтроллеров до достаточно сложных. Микроконтроллеры семейства MCS-51 позволяют выполнять как задачи управления различными устройствами, так и реализовывать отдельные узлы аналоговой схемы. Все микросхемы этого семейства работают с одной и той же системой команд, большинство из них выполняется в одинаковых корпусах с совпадающей цоколевкой (нумерация выводов для корпуса). Это позволяет использовать для разработанного устройства микросхемы разных фирм - производителей (таких какIntel, Dallas, Atmel, Philips и т.д.) без переделки принципиальной схемы устройства и программы.

MCS-51 выполнен по Гарвардской архитектуре, где адресные пространства памяти программ и данных разделены.

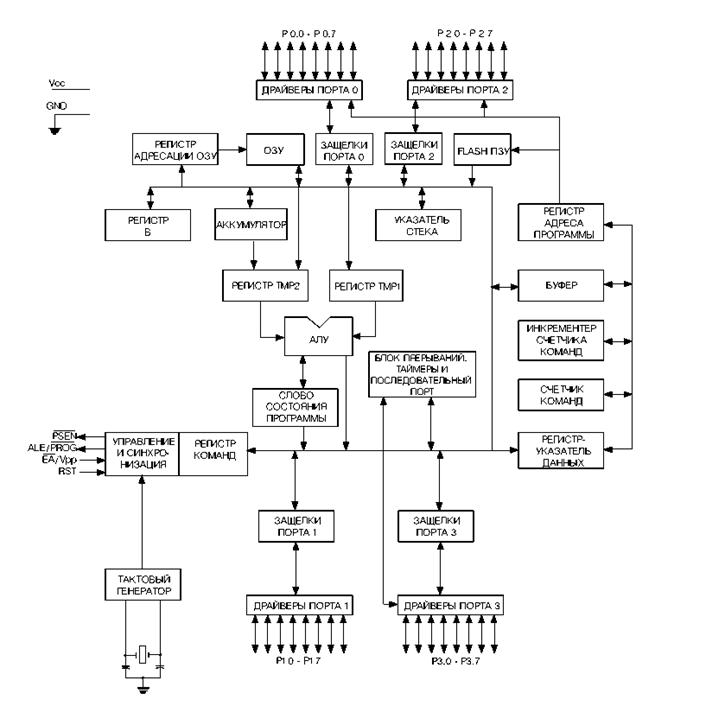

Структурная схема контроллера представлена на рис.2.3 и состоит из следующих основных функциональных узлов: блока управления, арифметико-логического устройства, блока таймеров/счетчиков, последовательного интерфейса и прерываний, программного счетчика (счетчика команд), памяти данных и памяти программ.

Двусторонний обмен осуществляется с помощью внутренней 8-разрядной магистрали данных. Рассмотрим подробнее назначение каждого блока. По такой схеме построены практически все представители семейства MCS-51. Различные микросхемы этого семейства различаются только регистрами специального назначения (в том числе и количеством портов). Система команд всех контроллеров семейства MCS-51 содержит 111 базовых команд с форматом 1, 2 или 3 байта и не изменяется при переходе от одной микросхемы к другой. Это обеспечивает прекрасную переносимость программ с одной микросхемы на другую.

Блок управления и синхронизации (Timing and Control) предназначен для выработки синхронизирующих и управляющих сигналов, обеспечивающих координацию совместной работы блоков ОЭВМ во всех допустимых режимах ее работы. В состав блока управления входят:

- устройство формирования временных интервалов,

- комбинационная схема ввода-вывода,

- регистр команд,

- дешифратор команд.

Входные и выходные сигналы блока управления и синхронизации:

1 PSEN – разрешение программной памяти;

2 ALE – выходной сигнал разрешения фиксации адреса;

3 PROG – сигнал программирования;

4 EA – блокировка работы с внутренней памятью;

5 VPP – напряжение программирования;

6 RST – сигнал общего сброса.

Устройство формирования временных интервалов необходимо для синхронизации последовательности состояний ЦП, образующих машинный цикл, а также для правильной работы всех внутреннихзащелок и выходных буферов портов. Машинный цикл состоит из шести последовательныхсостояний (States) от S1 до S6, каждое из которых, в свою очередь, подразделяется на две фазы:

фазу 1 (Phase 1 - P1) и фазу 2 (Phase 2 - P2). Таким образом, машинный цикл может быть определен как последовательность временных интервалов S1P1, S1P2, S2P1,....,S6P2. Длительность фазы равна периоду следования тактовых импульсов, поэтому машинный цикл занимает 12 тактовых периодов.

Количество машинных циклов определяет продолжительность выполнения команд. Практически все команды выполняются за один или два машинных цикла, кроме команд умножения и деления, продолжительность выполнения которых составляет четыре машинных цикла. Логика ввода - вывода предназначена для приема и выдачи сигналов, обеспечивающих обмен информации с внешними устройствами через порты ввода вывода Р0-Р3.

Регистр команд предназначен для записи и хранения 8-ми разрядного кода операции выполняемой команды. Код операции, с помощью дешифратора команд и логики управления ЭВМ, преобразуется в микропрограмму выполнения команды.

Рис 2.3. Структурная схема однокристального микроконтроллера Intel 8051

(семейство MCS-51)

Арифметико-логическое устройство (ALU) представляет собой параллельное восьмиразрядное устройство, обеспечивающее выполнение арифметических и логических операций. АЛУ состоит из:

- регистров временного хранения -TMP1 и TMP2,

- ПЗУ констант,

- сумматора,

- дополнительного регистра - регистра В,

- аккумулятора - ACC,

- регистра слова состояния программ (регистр флагов)- PSW.

Регистры временного хранения TMP1, TMP2 - восьмиразрядные регистры, предназначенные для приема и хранения операндов на время выполнения операций над ними. Эти регистры программно не доступны.

ПЗУ констант обеспечивает выработку корректирующего кода при двоично-десятичном представлении данных, кода маски при битовых операциях и кода констант.

Параллельный восьмиразрядный сумматор представляет собой схему комбинационного типа с последовательным переносом, предназначенную для выполнения арифметических операций сложения, вычитания и логических операций сложения, умножения, неравнозначности и тождественности.

Регистр B - восьмиразрядный регистр, используемый во время операций умножения и деления. Для других инструкций он может рассматриваться как дополнительный сверхоперативный регистр.

Аккумулятор - восьмиразрядный регистр, предназначенный для приема и хранения результата, полученного при выполнении арифметико-логических операций или операций сдвига.

Регистр состояния программ PSW (Programm Status Word) предназначен для хранения слова состояния выполняемых команд. При выполнении многих команд в ALU формируется ряд признаков операции (флагов), которые фиксируются в регистре слова состояния программы (PSW). В табл. 1 приводится перечень флагов PSW, даются их символические имена и описываются условия их формирования.

Блок прерываний и последовательного интерфейса - UART(Universal Asynchronous Receiver/Transmitter) предназначен для организации ввода - вывода последовательных потоков информации и организации системы прерывания программ.По определению прерывание означает временное прекращение основного процесса вычислений для выполнения некоторых запланированных или незапланированных действий, вызываемых работой аппаратуры или программы.

Эти действия могут носить сервисный характер, быть запросами со стороны программы пользователя на выполнение обслуживания либо быть реакцией на нештатные ситуации.

Табл. 1

| Символ | Разряд | Имя и назначение | |

| CY | PSW.7 | Флаг переноса. Устанавливается и сбрасывается аппаратно или программно при выполнении арифметических и логических операций | |

| AC | PSW.6 | Флаг вспомогательного переноса. Устанавливается и сбрасывается только аппаратно при выполнении команд сложения и вычитания и сигнализирует о переносе или займе в бите 3 | |

| F0 | PSW.5 | Флаг 0. Может быть установлен, сброшен или проверен программой как флаг, специфицируемый пользователем | |

| RS1 | PSW.4 | Выбор банка регистров. Устанавливается и сбрасывается программно для выбора рабочего банка регистров | |

| RS0 | PSW.0 | ||

| OV | PSW.2 | Флаг переполнения. Устанавливается и сбрасывается аппаратно при выполнении арифметических операций | |

| – | PSW.1 | Не используется | |

| P | PSW.0 | Флаг паритета. Устанавливается и сбрасывается аппаратно в каждом цикле и фиксирует нечетное/четное число единичных битов в аккумуляторе, т.е. выполняет контроль по четности | |

В состав блока входят:

1. логика управления,

2. регистр управления,

3. буфер передатчика,

4. буфер приемника,

5. приемопередатчик последовательного порта,

6. регистр приоритетов прерываний,

7. регистр разрешения прерываний,

8. логика обработки флагов прерываний и схема выработки вектора.

Счетчик команд (Program Counter) предназначен для формирования текущего 16-разрядного адреса внутренней памяти программ и 8/16-разрядного адреса внешней памяти программ. В состав счетчика команд входят 16-разрядные буфер РС, регистр РС и схема инкремента (увеличения содержимого на 1).

Память данных ОЗУ (RAM) предназначена для временного хранения информации, используемой в процессе выполнения программы.

Память программ (EPROM) предназначена для хранения программ и представляет собой постоянное запоминающее устройство (ПЗУ). В разных микросхемах применяются масочные, стираемые ультрафиолетовым излучением или FLASH ПЗУ.

Регистр указателя данных (DPTR) предназначен для хранения 16 - разрядного адреса внешней памяти данных.

Указатель стека (SP) представляет собой восьмиразрядный регистр, предназначенный для организации особой области памяти данных (стека), в которой можно временно сохранить любую ячейку памяти.

Порты P0, P1, P2, P3 являются квазидвунаправленными портами ввода - вывода и предназначены для обеспечения обмена информацией ОЭВМ с внешними устройствами, образуя 32 линии ввода- вывода.

Они предназначены для ввода или вывода информации побайтно. Каждый порт содержит управляемые регистр-защелку, входной буфер и выходной драйвер.

Выходные драйверы портов P0 и P2, а также входной буфер порта P0 используются при обращении к внешней памяти. При этом через порт P0 в режиме временного мультиплексирования сначала выводится младший байт адреса, а затем выдается или принимается байт данных. Через порт P2 выводится старший байт адреса в тех случаях, когда разрядность адреса равна 16 бит.

Все выводы порта P3 могут быть использованы для реализации альтернативных функций, перечисленных в табл. 2. Эти функции могут быть задействованы путем записи 1 в соответствующие биты регистра-защелки (P3.0 – P3.7) порта P3.

Р0 является двунаправленным, а Р1 – Р3 квазидвунаправленными. Каждая линия портов может быть использована независимо для ввода или вывода.

По сигналу RST в регистры-защелки всех портов автоматически записываются единицы, настраивающие их тем самым на режим ввода.

Все порты могут быть использованы для организации ввода/вывода информации по двунаправленным линиям передачи. Однако порты P0 и P2 не могут быть использованы для этой цели в случае, если система имеет внешнюю память, связь с которой организуется через общую разделяемую шину адреса/данных, работающую в режиме временного мультиплексирования.

Табл. 2

Альтернативные функции порта P3

| Символ | Разряд | Имя и назначение | ||

| RD | Р3.7 | Чтение. Активный сигнал низкого уровня формируется аппаратно при обращении к внешней памяти данных | ||

| WR | Р3.6 | Запись. Активный сигнал низкого уровня формируется аппаратно при обращении к внешней памяти данных | ||

| T1 | Р3.5 | Вход таймера/счетчика 1 или тест-вход | ||

| T0 | Р3.4 | Вход таймера/счетчика 0 или тест-вход | ||

| INT1 | P3.3 | Вход запроса прерывания 1. Воспринимается сигнал низкого уровня или срез | ||

| INT0 | Р3.2 | Вход запроса прерывания 0. Воспринимается сигнал низкого уровня или срез | ||

| TXD | Р3.1 | Выход передатчика последовательного порта в режиме UART*. Выход синхронизации в режиме регистра сдвига | ||

| RXD | Р3.0 | Вход приемника последовательного порта в режиме UART. Ввод/вывод данных в режиме регистра сдвига | ||

*Через универсальный асинхронный приемопередатчик UART происходят прием и передача информации, представленной последовательным кодом (младшими битами вперед) в полном дуплексном режиме обмена.

Организация памяти и функционирование микроконтроллера

Выполняя программу, микроконтроллер обрабатывает команду за командой. Команда задает выполняемую операцию и содержит сведения об участвовавших в ней операндах. После приема команды происходит ее расшифровка и выполнение, в ходе которого микроконтроллер получает необходимые данные из памяти или внешних устройств. Ячейки памяти и внешние порты имеют номера, называемые адресами, которыми они обозначаются в программе.

Таким образом, по однонаправленной адресной шине посылаются адреса, определяя объект, с которым будет обмен по шине данных (двунаправленной). По шине управления в разных направлениях передаются управляющие сигналы.

Микроконтроллеры семейства MCS-51 построены по Гарвардской архитектуре. Это означает, что память данных и память программ в этих микросхемах разделены и имеют отдельное адресное пространство. В этих микроконтроллерах имеется пять адресных пространств:память программ, внешняя память данных три для внутренней памяти. Такое построение памяти позволяет удвоить доступное адресное пространство. Кроме того такое построение памяти позволяет в ряде случаев увеличить быстродействие микросхем.

Память состоит из ячеек, каждой из которых присваивается свой адрес. Совокупность адресов, которые могут быть сформированы процессором, образует адресное пространство микроконтроллера. Адреса памяти могут занимать все адресное пространство или его часть, а линейно организованная память независимо от ее технической реализации может быть представлена набором регистров (ячеек), число которых M, а разрядность –N. Свои адреса имеют и внешние устройства. Процессор при обмене данными всегда должен выбрать только одну из ячеек памяти или одно внешнее устройство. Такой выбор осуществляется схемами декодирования адреса. При управлении памятью и внешними устройствами процессор должен вначале сформировать нужный адрес, который затем декодируется.

Применяется несколько способов формирования адресов.

При прямой адресации код адреса содержится в команде, подлежащей выполнению. Прямая адресация удобна, но удлиняет команды (увеличивает их разрядность), т. к. при больших емкостях памяти разрядности адресов достаточно велики. В случае прямой регистровой адресации, когда операнд находится в одном из внутренних регистров процессора, адрес является малоразрядным, поскольку число таких регистров мало. В этом случае прямая адресация проявляет все свои достоинства.

При косвенной адресации в команде явно или неявно указывается адрес регистра процессора, содержащий сведения об адресе операнда. Команда сохраняет компактность, но для ее выполнения требуется предварительная настройка – загрузка сведений в регистр косвенного адреса (индексный регистр). Косвенная адресация удобна при обработке списков, когда настройка производится однократно, а очередной адрес получается модификацией предыдущего (изменением его на единицу). В зависимости от действий, которые производятся над содержимым индексного регистра при формировании адреса, различают несколько видов косвенной адресации:

- простая, когда обращение к ячейке памяти осуществляется по адресу, находящемся в индексном регистре, т. е. никаких действий над его содержимым не проводится;

- относительная, когда адрес образуется суммированием содержимого индексного регистра и числа, задаваемого в команде. Существуют и другие разновидности косвенной адресации.

- при непосредственной адресации в команде содержится сам операнд.

Возможность использования различных видов адресации сокращает объем и время выполнения программ.

С помощью того или иного способа адресации формируется физический адресный код, поступающий на шину адреса для выбора ячейки памяти или внешнего устройства с которы в данный момент взаимодействует процессор.

Адресация может быть абсолютной или неабсолютной. При абсолютной адресации обратиться к ячейке памяти или внешнему устройству можно только по одному единственному адресу. При неабсолютной адресации для ячейки памяти или внешнего устройства выделяется некоторая зона адресов. Число таких зон, естественно, будет меньше, чем число отдельных адресов, поэтому для указания зоны потребуется меньшая разрядность адреса.

Структура внутренней памяти данных рассматриваемого микроконтроллера представлена на рис. 2.4.

Рис. 2.4. Структура внутренней памяти данных MCS-51

Внутренняя память данных всегда адресуется байтом, что подразумевает 256 байт адресного пространства. Однако фактически можно обращаться к 384-м байтам. Прямая адресация ячейки с адресом свыше 7Fh осуществляет доступ к области регистров специальных функций, а косвенная - к верхней области внутренней памяти данных. Т.о. эти две области занимают одно и то же адресное пространство, хотя и разделены физически. Все байты в нижней 128-байтной половине внутренней памяти данных могут адресоваться как прямо, так и косвенно.

Первые 32 байта в нижней области внутреннего ОЗУ сгруппированы в 4 банка по 8 регистров. Инструкции программы могут оперировать с ними как с регистрами общего назначения R0-R7. Два бита регистра PSW определяют, какой из банков используется в текущий момент. Это позволяет более эффективно использовать память программ, поскольку регистровые инструкции короче, чем прямая адресация. Переключение регистровых банков эффективно заменяет операции сохранения регистров в стеке на время обработки прерывания.

Следующие за регистровыми банками 16 байт образуют блок побитно адресуемого пространства. Набор инструкций MCS-51 содержит широкий набор операций над битами, а 128 бит (16 байт по 8) в этом блоке могут быть прямо адресованы. Битовые адреса имеют значения от 00h до 7Fh.

Для 16 адресов в пространстве SFR (регистры специальных функций) имеется возможность как битовой, так и байтовой адресации. Побитово-адресуемыми регистрами являются те, чей шестнадцатеричный адрес заканчивается на “0” или “8”. Битовые адреса в этой области располагаются со значения 80h по FFh.

Наиболее часто используемыми регистрами специальных функций являются:

- Аккумулятор (байтовый адрес 0E0h). Используется во всех арифметических и логических операциях в качестве операнда;

- Регистр B (байтовый адрес - 0F0h). Используется при операциях умножения и деления, а также как сверхоперативный регистр;

- Слово состояния программы PSW (байтовый адрес - 0D0h). Содержит информацию о состоянии программы;

- Указатель стека (байтовый адрес -081h). Используется для указания на вершину стека в операциях записи в стек и чтения из него. По аппаратному сбросу устанавливается в значение 07h (область стека в этом случае начинается с адреса 08h) и инкрементируется при каждой записи в стек. Запись в SP производится для предопределения положения стека во внутренней памяти данных микроконтроллера;

- Указатель данных DPTR (байтовые адреса 082h, 083h). Состоит из двух байт: старшего - DPH и младшего - DPL. Используется как 16-ти или 8-битовый указатель адреса при обращении к внешней памяти или выполнении команды перехода по косвенному адресу.

Память программ предназначена для хранения программ и имеет отдельное от памяти данных адресное пространство объемом 64 Кбайт, причем для некоторых микросхем (например КР1816ВЕ51, КМ1819ВЕ751, КР1830ВЕ51) для хранения программ на кристалле микроконтроллера расположено ПЗУ. Это ПЗУ отображается в область млаших адресов памяти программ. Учитывая, что выполнение программы после сброса микроконтроллера всегда начинается с нулевого адреса памяти программ, то при включении питания начнет выполняться программа, записанная во внутненнем ПЗУ микроконтроллера. Микроконтроллеры, не имеющие внутреннего ПЗУ (например КР1816ВЕ31 и КР1830ВЕ31) могут работать только с внешней микросхемой ПЗУ емкостью до 64 Кбайт (при использовании портов P1 и P3 в качестве расширителя адреса объем подключаемой ПЗУ может быть увеличен до 1Гбайта). Микроконтроллеры семейства MCS-51 имеют внешний вывод EA, с помощью которого можно запретить работу внутренней памяти, для чего необходимо подать на вывод EA логический "0" (соединить этот вывод с корпусом). При этом внутренняя память программ отключается и, начиная с нулевого адреса, все обращения происходят к внешней памяти программ.

Доступ к внешней памяти программ осуществляется в двух случаях:

1. при действии сигнала EA=0 независимо от адреса обращения,

2. в любом случае, если программный счетчик (РС) содержит число большее, чем максимальная ячейка внутренней памяти программ.

Распределение памяти программ микроконтроллера АТ89С52 представлено ниже:

Для других микроконтроллеров этого семейства изменяется только объем внутренней памяти программ и количество доступных векторов прерываний программы.

| Для чтения памяти программ используются команды MOVC A, A+@DPTR и MOVC A, A+@PC |

Рис. 2.5. Адресное пространство памяти программ.

Ниже приведены адреса векторов прерываний и соответствующие им аппаратурные источники прерываний программы:

| Вектор прерывания | Флаги, вызывающие прерывание | Источник прерывания |

| 0000Н | - | Рестарт (сброс) контроллера RESET |

| 0003Н | IE0 | внешнее прерывание INT0 |

| 000bН | TF0 | Таймер 0 |

| 0013Н | IE1 | внешнее прерывание INT1 |

| 001bН | TF1 | Таймер 1 |

| 0023Н | RI, TI | Последовательный порт |

| 002bН | TF2, EXF2 | Таймер 2 |

| 0033Н | CF, CCFn(n=0:4) | Набор программируемых счётчиков (РСА) |

| 003bН | AIF | Аналого-цифровой преобразователь |

| 0043Н | CF1,C1CCFn(n=1:4) | Набор программируемых счётчиков (РСА1) |

| 004bН | SEPIF | Последовательный порт SEP |

| 0053Н | IE2 | внешнее прерывание INT2 |

| 005bН | IE3 | внешнее прерывание INT3 |

| 0063Н | IE4 | внешнее прерывание INT4 |

| 006bН | IE5 | внешнее прерывание INT5 |

| 0073Н | IE6 | внешнее прерывание INT6 |

Примечание: вектора прерывания, выделенные:

- жирным подчеркнутым текстом - присутствуют во всех микросхемах семейства;

- жирным текстом- отсутствуют в микросхемах 8051,8031, КР1816ВЕ31, КР1816ВЕ51, КР1816ВЕ751 КР1830ВЕ31, КР1830ВЕ51, КР1830ВЕ751;

- обычным текстом- присутствуют только в микросхемах 8Х51FA, FB, FC и GB

- курсивом - присутствуют только в микросхеме 8Х51GB

Система команд микроконтроллера предоставляет большие возможности обработки данных, обеспечивает реализацию логических, арифметических операций, а также управление в режиме реального времени.

Реализована побитная, потетрадная (4 бита), побайтовая (8 бит) и 16-разрядная обработка данных. Микросхемы семейства MCS-51 - это 8-разрядные микропроцессоры, а это означает, что ПЗУ, ОЗУ, регистры специального назначения, АЛУ и внешние шины имеют байтовую организацию.

Двухбайтовые данные используются только регистром-указателем (DPTR) и счетчиком команд (PC).

В машинном коде команда занимает один, два или три байта в зависимости от типа адресации.

Команды выполняются за один, два или четыре (умножение и деление) машинных цикла.

Все множество команд, выполняемых микроконтроллером, можно разбить на следующие группы:

● команды пересылки данных;

● команды арифметических операций;

● команды логических операций;

● команды операций с битами;

● команды передачи управления;

● команды управления системой (специальные команды).

2014-02-13

2014-02-13 5547

5547