Микропроцессор - это программно-управляемое электронное устройство, предназначенное для цифровой обработки информации и управления процессом этой обработки, и реализованное в виде одной или нескольких интегральных микросхем (ИМС).

1.9. Архитектура современных ЭВМ.

Классификация аппаратных средств вычислительных систем по Ф.Г. Энслоу.

В основу классификации многопроцессорных вычислительных систем (МВС), предложенной Ф.Г. Энслоу, положены разновидности топологии соединительной сети и методы ее работы, определяющие метод соединения аппаратных модулей в единую многопроцессорную вычислительную систему. Эта классификация учитывает степень параллельности потоков информации степень и возможность одновременной работы модулей МВС. Предполагается, что МВС сосредоточена в одном месте таким образом, что расстояния между отдельными ее модулями позволяют передавать информацию со скоростью, согласующейся с производительностью процессоров и пропускной способностью остальных элементов.

Согласно классификации Ф.Г. Энслоу существует несколько типов структурной организации МПВК:

· с общей шиной;

· с перекрестной коммутацией;

· с многовходовыми ОЗУ;

· ассоциативные;

· матричные и векторные,

· конвейерной обработкой.

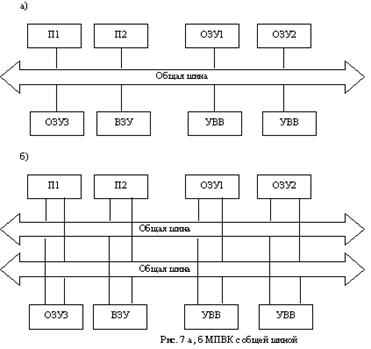

1. С общей шиной.

В комплексах с общей шиной проблема связей всех устройств между собой решается крайне просто: все они соединяются общей шиной, выполненной в виде совокупности проводов или кабелей, по которым передаются информация, адреса и сигналы управления (рис. 7 а). Интерфейс является односвязным, т.е. обмен информацией в любой момент времени может происходить только между двумя устройствами. Если потребность в обмене существует более чем у двух устройств, то возникает конфликтная ситуация, которая разрешается с помощью системы приоритетов и организации очередей в соответствии с этим. Обычно функции арбитра выполняет либо процессор, либо специальное устройство, которое регистрирует все обращения к общей шине и распределяет шину во времени между всеми устройствами комплекса.

Несомненные достоинства структуры с общей шиной - простота, в том числе изменения комплекса, добавления или изъятия отдельных устройств, а также доступность модулей ОЗУ для всех остальных устройств. Следствием всего этого является достаточно низкая стоимость комплекса.

Вместе с тем комплексы с общей шиной не лишены определенных недостатков. Первый - невысокое быстродействие, так как одновременный обмен информацией возможен между двумя устройствами, не более. По этой причине в комплексах с общей шиной число процессоров не превосходит двух-четырех. Этот недостаток может быть несколько компенсирован путем использования общей шины с высоким быстродействием, большим, чем быстродействие входящих в комплекс устройств. Однако этот путь приводит к усложнению и удорожанию комплекса. Второй недостаток МПВК с общей шиной заключается в относительно низкой надежности системы из-за наличия общего элемента - шины. Надо иметь в виду, что надежность общей шины определяется не только надежностью проводов и кабелей (их собственная надежность достаточно высока), но и надежностью всех соединений, входных и выходных цепей устройства. Отказ хотя бы одного из элементов приводит к отказу всего комплекса. Этот недостаток можно компенсировать за счет введения резервной шины (рис. 7,б). Хотя это несколько усложняет комплекс, однако надежность его существенно возрастает. Если же резервную шину сделать активной, т. е. работающей одновременно с основной, то можно не только повысить надежность, но и увеличить производительность комплекса за счет того, что обмен информацией может осуществляться одновременно между двумя парами устройств.

Общая шина может быть организована различными способами - принципиально так же, как и для однопроцессорных ЭВМ с общей шиной. Характерным примером является комплекс СМ-1420, в котором используется общая шина однопроцессорных ЭВМ этой системы.

2. С перекрестной коммутацией.

Мультипроцессорные системы, построенные по принципу осуществления связей между модулями посредством "прямоугольной решетки" соединительных шин, которые могут контактировать в любой точке их пересечения, называют системами с перекрестной коммутацией.

Такая организация системы позволяет устанавливать контакт между любыми двумя блоками системы на все время обмена информацией. В отличие от коммутации с временным разделением, реализуемым в системах с общей шиной, рассматриваемый метод переключения связей часто называют коммутацией с пространственным разделением.

Перекрестный коммутатор является "неблокирующимся" в том смысле, что передача через него может быть запрещена из-за отсутствия путей передачи. Существует возможность установить одновременно несколько путей передачи информации в системе. В то же время следует иметь в виду, что коммутатор может быть заблокирован, если одно из соединяемых устройств уже занято.

Одной из ранних структур, в которой реализован принцип перекрестной коммутации, явилась система, получившая название "полиморфная ЭВМ". Модули ЭВМ, включающие блоки процессоров и памяти, могли осуществлять связь с периферийными устройствами через центральный коммутатор.

В данной системе была сделана попытка организовать соединения непосредственно между процессорами и перекрестный доступ к памяти путем замыкания соответствующего набора пересечений. Сложность такого способа связи между процессорами и блоками памяти, неэффективность использования оборудования (процессор и память одного единственного модуля, имея единственную шину связи, "мешают" друг другу) выявляют недостатки структуры "полиморфной ЭВМ" по сравнению со структурой системой.

Мультипроцессорные системы с перекрестной коммутацией, обладая несколько меньшей гибкостью, чем системы с общей шиной, позволяют тем не менее сравнительно просто вводить новые модули, если коммутационная матрица обладает достаточной емкостью. Матрица полностью отделена от других функциональных блоков и может быть построена также но модульному принципу, что допускает ее расширение. Однако вследствие сложности функций коммутатора, структура его может существенно усложниться.

Для обеспечения большей гибкости и увеличения возможностей по расширению в системе может быть введена дополнительная коммутационная матрица устройств ввода-вывода. Такой коммутатор связывается с центральным через процессоры управления вводом-выводом, при этом устройства ввода- вывода могут подсоединяться к любому каналу.

3 МПВК с многовходовыми ОЗУ.

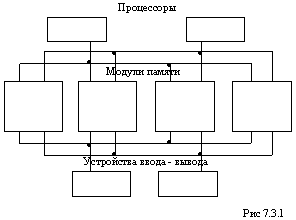

Как и системы, описанные в предыдущем параграфе, мультипроцессоры с многовходовой памятью используют несколько путей одновременной передачи информации (рис. 3.1). Такая топология схемы соединений более экономична, чем конфигурация с перекрестным коммутатором, так как в ней, вообще говоря, меньше точек, в которых могут возникать конфликты, требующие разрешения. Модули памяти в мультипроцессорах данного типа должны иметь по нескольку входов.

Кроме того, блоки памяти должны быть снабжены логическими схемами, предназначенными для разрешения конфликтов, в тех случаях, когда несколько процессоров или внешних устройств требуют одновременного доступа к одному и тому же модуле оперативной памяти. Таким образом, в системах с многовходовой памятью каждый модуль памяти должен идентифицировать и обрабатывать запросы на доступ к определенным ячейкам памяти. Устройство управления памятью при этом разрешает конфликты при одновременном обращении и сообщает обратившемуся к модулю памяти устройству системы, что ему разрешен доступ к данному модулю.

Максимально возможная конфигурация в мультипроцессорax рассматриваемого типа ограничена числом входов модулей памяти Наращивание дан. ной конфигурации возможно путем использования мультиплексоров на входе модулей оперативной памяти, однако скорость передачи данных в такой системе не выше скорости передачи при отсутствии мультиплексоров.

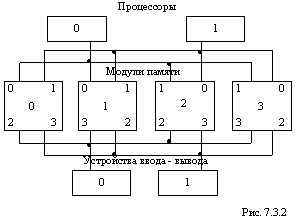

Необходимо отметить, что входы модуля памяти в системах рассматриваемого типа могут обладать разными приоритетами, обусловленными различием точек физических (электрических) соединений. Эта особенность может быть использована для разрешения конфликтов при одновременных запросах. Приоритет в таком случае отдается процессору или внешнему устройству, обращающемуся к "своему" модулю памяти (рис. 3.2).

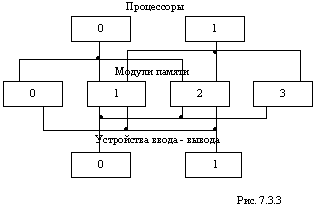

Существуют конфигурации мультипроцессорных систем с многовходовой памятью, в которых каждый процессор имеет "собственную" память (рис. 3.3). В собственной памяти могут храниться, например, специальные таблицы операционной системы, необходимые при реализации функций управления, распределения ресурсов, восстановления и т. п. Однако если каждый процессор не имеет доступа к любому модулю памяти, универсальность мультипроцессорной системы утрачивается. При этом существенно уменьшается гибкость функционирования операционной системы и перемещения в памяти объектных программ.

Если, например, какой-либо процессор вышел из строя и прерванную работу необходимо закончить с помощью другого процессора, то может оказаться, что новому процессору будет недоступна информация, необходимая для выполнения этой задачи. Аналогичные трудности может вызвать также выход из строя модуля собственной памяти некоторого процессора. Таким образом, конфигурацию с собственной памятью отличает более низкая надежность системы.

В системах с многовходовой памятью, как и в мультипроцессорах с коммутатором, ширина пути передачи данных определяется экономичностью и производительностью. Если основной единицей хранения данных является слово, а ширина пути передачи информации меньше слова, то интерфейс должен содержать специальную аппаратуру для упаковки и распаковки слов. Эта аппаратура должна также следить за тем чтобы путь передачи не был разорван, пока передача слова не будет закончена, и чтобы а него не была введена другая информация.

4. Ассоциативные ВС.

Исследования производителей вычислительной техники показали, что системы обработки информации, поступающей от многих датчиков, системы слежения за многими движущимися объектами и другие специализированные системы обработки наиболее эффективно могут быть реализованы на структурах аппаратных средств, обладающих свойствами ассоциативности и параллельности.

Понятие "ассоциативная система" означает, что обработка данных в системе может производиться не только обычными средствами адресации, указывающими на местоположение единиц информации в памяти, но и путем идентификации и выбора данных по их содержанию. Структура такой вычислительной системы основывается на использовании ассоциативной памяти, дополнительная логика которой обеспечивает адресацию слов по содержанию.

Принцип ассоциативного обращения к информации может быть использован при приеме и размещении в памяти входных потоков данных с целью последующего выбора всех слов с заданными свойствами для выходных потоков. На базе ассоциативной памяти реализуются также функции, связанные с перестроением данных, т.е. изменением места и порядка расположения элементов информации.

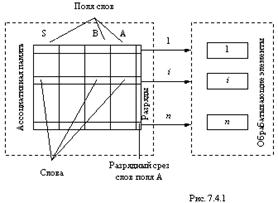

Итак, высокая степень параллельности обработки может быть достигнута тогда, когда одноименные операции выполняются одновременно над всем множеством содержащихся в выделенном поле ассоциативной памяти слов. Для этого в состав ассоциативной вычислительной системы вводятся обрабатывающие элементы, реализующие арифметическую и логическую обработку информации. Упрощенная структура связки ассоциативная память - обрабатывающие элементы (ОЭ) представлена на рис.4.1.

Достижение наивысшей степени параллельности обработки возможно, когда число ОЭ соответствует числу обрабатываемых слов. При этом, если они (слова) обрабатываются последовательно поразрядно, то в текущий момент времени элементы (ОЭ) обрабатывают разрядный срез всех слов данных.

5. Матричные системы.

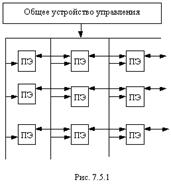

Если не считать машины Унгера (1958г.), которая была узкоспециализированной и предназначалась только для решения задач распознавания образов, то, по-видимому, первой матричной системой следует считать систему SOLOMON. Система содержит 1024 ПЭ, соединенных в виде матрицы 32Х32. Каждый ПЭ в матрице соединен с четырьмя соседними и включает в себя процессор, обеспечивающий выполнение последовательных поразрядных арифметических и логических операций, а также оперативное ЗУ емкостью 16 кбит, разбитое на модули по 4 кбит каждый. Длина слова переменная - от 1 до 128 разрядов. Разрядность слов устанавливается программно. По каналам связи от УУ передаются команды и общие константы. В ПЭ используется так называемая многомодальная логика, которая позволяет каждому ПЭ выполнять (т.е. быть активным) или не выполнять (быть пассивным) общую операцию в зависимости от значений обрабатываемых данных.

В каждый момент все активные ПЭ выполняют одну и ту же операцию над данными, хранящимися в собственной памяти и имеющими один и тот же адрес. Идея многомодальности заключается в том, что в каждом ПЭ имеется специальный регистр на четыре состояния - регистр моды.

Мода (или модальность) заносится в этот регистр от УУ. При выполнении последовательности команд модальность передается в коде операции и сравнивается с содержимым регистра моды. Если есть совпадение, то операции выполняется. В других случаях ПЭ не выполняет операцию, но может в зависимости от кода пересылать свои операнды соседнему ПЭ. Такой механизм позволяет, в частности, выделить строку или столбец ПЭ, что может быть полезным при операциях над матрицами. Взаимодействуют ПЭ с периферийным оборудованием через внешние ПЭ.

2015-01-21

2015-01-21 2466

2466