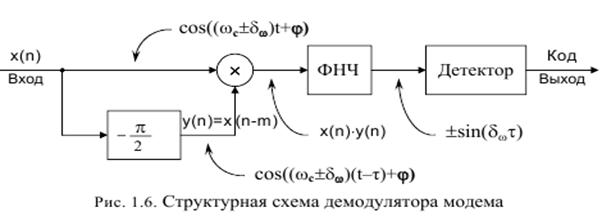

Задачей демодулятора является определение частоты принимаемого сигнала и формирование соответствующего цифрового кода. Для этого можно применить, например, аналоговую или цифровую фильтрацию. Но, учитывая небольшую разницу частот «1» и «0», а также малую выборку сигнала с одной

частотой, данный метод является неэффективным.

Другой метод основан на перемножении двух сигналов, принятого и задержанного на некоторое время (формула произведения двух углов).

Согласно выражению (1) принятый из канала сигнал в момент времени t = n ⋅Δt

x(n) = cos((ωc±δω)n+ϕ). (6)

Этот сигнал умножается на такой же, но задержанный на τ = m ⋅Δt сигнал

y(n) = x(n–m) = cos((ωc±δω)(n–m)+ϕ), (7)

где τ – время задержки, Δt – период дискретизации.

В результате после умножения получаем

2 ⋅ x (t) ⋅ x(t–τ) = 2 ⋅ cos[(ωc±δω)t+ϕ] ⋅ cos[(ωc±δω)(t–τ)+ϕ] = cos[2(ωc±δω)t–(ωc±δω)τ+2ϕ] + cos[(ωc±δω)τ].

Если положить, что ωc ⋅ τ = π/2, то после низкочастотной фильтрации (ФНЧ) удвоенной несущей частоты ωc получается

cos[(ωc±δω)τ] = cos(π/2±δωτ) = –sin(±δωτ) = –[±sin(δωτ)]. (8)

Отсюда следует, что по знаку сигнала после низкочастотной фильтрации (в блоке детектора) можно определить значение передаваемой информации. Отрицательный результат соответствует передаче «0», а положительный – «1».

Принимая во внимание, что фазовая задержка задана как ωc ⋅ τ = π/2, можно определить величину τ = π/2ωc = 1/4fc. Для частоты fc = 1700 Гц величина τ = 147.06 мкс, что примерно в 1.5 раза больше периода дискретизации Δt = 104.167 мкс. Для минимизации ошибки детектирования сигнала необходимо как можно точнее задать задержку π/2.

Таким образом, структурная схема демодулятора имеет следующий вид (рис. 1.6):

Сигнал с выхода фильтра (фазовращателя) y(n) после умножения на входной сигнал демодулятора x(n) поступает на вход ФНЧ. В качестве ФНЧ используется двухкаскадный цифровой элиптический рекурсивный фильтр второго порядка.

Частота пропускания определяется скоростью передачи информации (V):

Fp = (V / fН) = (1200 / 4800) = 0,25, (13)

а частота подавления – удвоенной минимальной частотой принимаемого сигнала (2f1):

Fa = (2 f1) / fН = (2 ⋅ 1300) / 4800 = 0,54. (14)

Передаточная функция одного каскада описывается уравнением

y(n) = a0⋅x(n)+a1⋅x(n–1)+a2⋅x(n–2)–b1⋅y(n–1)–b2⋅y(n–2).

Последним элементом демодулятора является детектор, который путем подсчета числа положительных и отрицательных отсчетов сигнала после ФНЧ за время передачи одного бита информации определяет, какой бит «1» или «0» был передан.

Для синхронизации приемника и передатчика каждое слово данных сопровождается битами синхронизации. Передача начинается всегда со “стартового бита”, который обычно равен «0», а заканчивается одним или двумя “стоповыми битами”, обычно равными «1». При отсутствии передачи данных в линию обычно передаются посылки, соответствующие передаче «1».

2015-02-04

2015-02-04 1392

1392