Двоично-десятичные счетчики реализуют счет импульсов в десятичной системе счисления, причем каждая десятичная цифра от нуля до девяти кодируется четырехразрядным двоичным кодом (тетрадой). Эти счетчики часто называют десятичными или декадными, поскольку они работают с модулем счета, кратным десяти.

Многоразрядный двоично-десятичный счетчик строится на основе регулярной цепочки декад, при этом первая (младшая) декада имеет вес 10°, вторая — 101, третья —102 и т.д.

Декада строится на основе четырехразрядного двоичного счетчика, в котором исключается избыточное число состояний. Исключение лишних шести состояний в декаде достигается многими способами:

• предварительной записью числа 6 (двоичный код 0110); после счета девятого импульса выходной код равен 1111 и десятичный сигнал возвращает счетчик в исходное состояние 0110. Таким образом, здесь результат счета фиксируется двоичным кодом с избытком 6;

• блокировкой переносов: счет импульсов до девяти осуществляется в двоичном коде, после чего включаются логические связи блокировки переносов; с поступлением десятого импульса счетчик заканчивает цикл работы и возвращается в начальное нулевое состояние;

• введением обратных связей, которые обеспечивают счет в двоичном коде и принудительное переключение счетчика в нулевое начальное состояние после поступления десятого импульса.

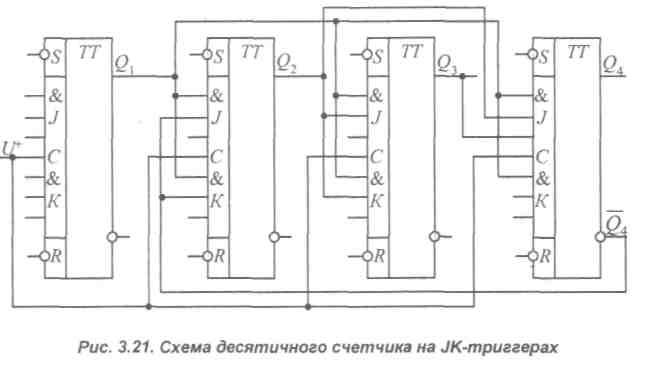

Схема синхронного десятичного счетчика с блокировкой переносов показана на рис. 5.20.

Рисунок 5.20-Схема десятичного счетчика на JK-триггерах

В этой схеме С-входы используются как счетные. С приходом десятого импульса на С-вход младшего разряда JK-триггера обнуляются первый и четвертый разряды и сигналом с выхода Q4 блокируют переключения второго и третьего разряда. Схема суммирующего счетчика с обратными связями (один разряд) показана на рис. 5.21.

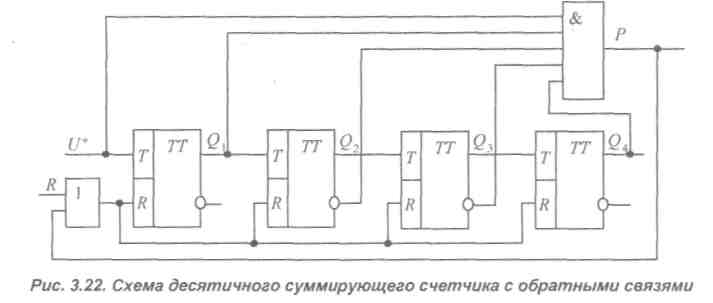

Рисунок 5.21-Схема десятичного суммирующего счетчика cобратными связями

После сброса в нулевое начальное состояние на счетный вход первого триггера поступают суммируемые импульсы U+. Сигналы переноса в старшие разряды формируются обычным асинхронным способом. Счет до девяти ведется в двоичном коде.

После прихода десятого входного импульса обратная связь на основе схемы совпадения вырабатывает сигнал P=U+Q4Q3Q2Ql, который является переносом для старшей декады и одновременно переключает счетчик в нулевое состояние.

Далее цикл работы счетчика повторяется.

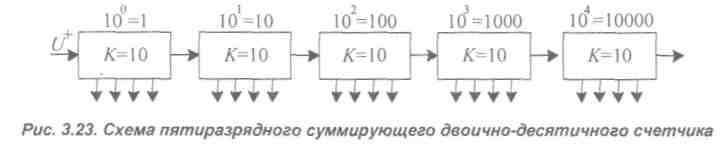

Схема пятиразрядного суммирующего двоично-десятичного счетчика показана на рис. 5.22.

Рисунок 5.22-Схема пятиразрядного суммирующего двоично-десятичного счетчика

Модуль данного счетчика составляет Ксч = 105 = 100000, емкость счета AU = Ксч - 1= 99999.

Выходы триггеров каждой декады подключаются ко входам дешифраторов, которые обеспечивают визуальную индикацию состояния счетчика с помощью разного рода световых табло.

2015-03-22

2015-03-22 11003

11003