Регистрами называют логические устройства, предназначенные для запоминания и хранения цифровых кодов. Построение регистров выполняют на триггерах. Операцию передачи цифрового кода в регистр и из регистра можно осуществлять последовательно и параллельно.

Рис.10.23. Логическая схема дешифратора

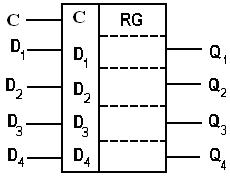

На рис.10.24 изображено условное обозначение и схема четырёхразрядного регистра параллельного действия, построенного на синхронных D – триггерах. Регистр имеет четыре входа D1÷D4 информационных и один синхронизирующий вход С.

B исходное нулевое состояние логических сигналов на всех выходах Q1 ÷ Q4,

регистр устанавливается при подаче на синхронизирующий вход С сигнала лог. 1 и на все информационные входы D сигнала лог “0”. Запись двоичного числа производится при одновременной подаче на информационные входы D1÷D4 кода числа.

Рис.10.24. Условное обозначение и схема четырёхразрядного регистра параллельного действия

Триггеры, на информационные входы которых подаются сигналы лог. 1, переводятся в состояния 1, остальные останутся в состоянии 0. Записанное число считывается с выходов Q1÷Q4.

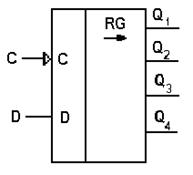

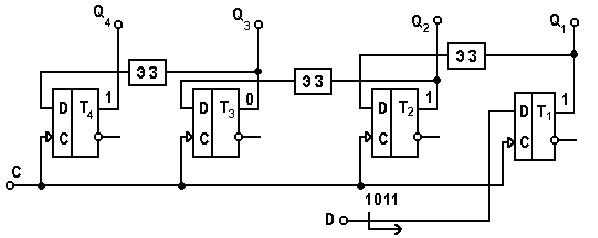

Для запоминания числа и сдвига влево используется схемы сдвигающего регистра. На рис.10.25 приведено условное обозначение и логическая схема сдвигающего регистра. Регистры такого типа используют в качестве преобразователей последовательного кода в параллельный код.

Регистр имеет два входа: на вход С поступают динамические импульсы сдвига, являющимися положительными импульсами, изменяющимися во времени; вход D является информационным входом.

При записи числа в сдвигающий регистр цифровой двоичный код подается на информационный вход D триггера Т1, начинается со старшего разряда. При этом положительные импульсы сдвига поступают на счётные входы С триггеров.

Работу регистра рассмотрим на примере записи числа 1011. С приходом импульса сдвига на вход С и подаче на вход D единицы старшего разряда числа, триггер Т1 переводится в состояние 1 (Q1). В регистре используются элементы задержки ЭЗ, которые осуществляют задержку во времени перемещения сигнала с одного триггера на другой. При подаче очередного импульса сдвига на вход С и подаче на вход D второго разряда (нуля) числа, на выходе Q1 появится 0, а 1 из триггера Т1 через элемент ЭЗ переместится в триггер Т2. С приходом очередного импульса сдвига на вход С и подаче на вход D третьего разряда (единицы) числа, триггер Т1 установится в 1 и т.д. Путём последовательной подачи кодов чисел на вход D и импульсов сдвига на вход С, число записывается в регистр.

Рис.10.25. Условное обозначение и логическая схема сдвигающего регистра

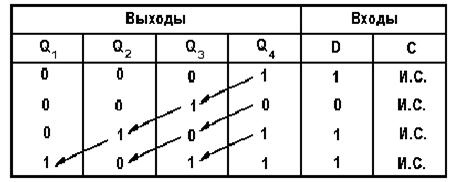

Считывание чисел осуществляется параллельным кодом с выходов Q1 ÷ Q4 или последовательным кодом с выхода Q4 путем последовательной подачи импульсов сдвига. На рис.10.26 приведена таблица истинности сдвигающего регистра.

Рис.10.26. Таблица истинности сдвигающего регистра

2015-04-01

2015-04-01 6011

6011