Mov EAX,0FFFFFFFFh; Работа с двойным словом (32 бита)

Mov BX,0FFFFFFFFh; Работа со словом (16 бит)

mov CL,0FFh; Работа с байтом (8 бит)

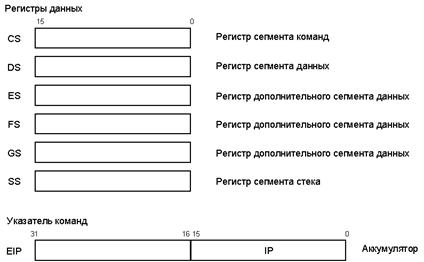

Рисунок 1.2 – Сегментные регистры и указатель команд

Все сегментные регистры, как и в процессоре 8086, являются 16-разрядными. В их состав включено еще два регистра – FS и GS, которые могут использоваться для хранения сегментных адресов двух дополнительных сегментов данных. Таким образом, при работе в реальном режиме из программы можно обеспечить доступ одновременно к четырем сегментам данных, а не к двум, как при использовании МП 8086.

Регистр указателя команд также является 32-разрядным и обычно при описании процессора его называют EIP. Младшие шестнадцать разрядов этого регистра соответствуют регистру IP процессора 8086.

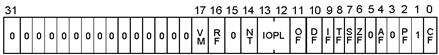

Регистр флагов процессоров, начиная с 486 принято называть EFLAGS. Дополнительно к шести флагам состояния (CF, PF, AF, ZF, SF и OF) и трем флагам управления состоянием процессора (TF, IF и DF), назначение которых было описано в предыдущих пособиях, он включает три новых флага NT, RF и VM и двухбайтовое поле IOPL (рисунок 1.3).

Рисунок 1.3 – Регистр флагов EFLAGS

Новые флаги NT, RF и VM, а также поле IOPL используются процессором только в защищенном режиме.

Двухразрядное поле привилегий ввода-вывода IOPL (Input/Output Privilege Level) указывает на максимальное значение уровня текущего приоритета (от 0 до 3), при котором команды ввода-вывода выполняются без генерации исключений.

Флаг вложенной задачи NT (Nested Task) показывает, является ли текущая задача вложенной в выполнение другой задачи. В этом случае NT =1. Флаг устанавливается автоматически при переключении задач. Значение NT проверяется командой iret для определения способа возврата в вызвавшую задачу.

Управляющий флаг рестарта RF (Restart Flag) используется совместно с отладочными регистрами. Если RF =1, то ошибки, возникшие во время отладки при исполнении команды, игнорируются до выполнения следующей команды.

Управляющий флаг виртуального режима VM (Virtual Mode) используется для перевода процессора из защищенного режима в режим виртуального процессора 8086. В этом случае процессор функционирует как быстродействующий МП 8086, но реализует механизмы защиты памяти, страничной адресации и ряд других возможностей.

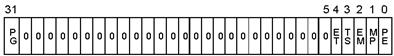

При работе с процессором программист имеет доступ к четырем управляющим регистрам CR0...CR3, в которых содержится информация о состоянии компьютера. Эти регистры доступны только в защищенном режиме для программ, имеющих уровень привилегий 0. Нас будет интересовать лишь регистр CR0 (рисунок 1.4), представляющий собой слово состояния системы. Более подробно этот управляющий регистр будет рассмотрен в следующей главе.

Для управления режимом работы процессора и указания его состояния используются следующие шесть битов регистра CR0:

Рисунок 1.4 – Управляющий регистр CR0

Бит страничного преобразования PG (Paging Enable). Если этот бит установлен, то страничное преобразование разрешено; если сброшен, то запрещено.

Бит типа сопроцессора ЕТ (Extension Туре) в МП 80286 и 80386 указывал на тип подключенного сопроцессора. Если ЕТ = 1, то 80387, если ЕТ = 0, то 80287. В более новых процессорах бит ЕТ всегда установлен.

Бит переключения задачи TS (Task Switched). Этот бит автоматически устанавливается процессором при каждом переключении задачи. Бит может быть очищен командой clts, которую можно использоваться только на нулевом уровне привилегий.

Бит эмуляции сопроцессора ЕМ (Emulate). Если ЕМ = 1, то обработка команд сопроцессора производится программно. При выполнении этих команд или команды wait генерируется исключение отсутствия сопроцессора.

Бит присутствия арифметического сопроцессора MP (Math Present). Операционная система устанавливает МР = 1, если сопроцессор присутствует. Этот бит управляет работой команды wait, используемой для синхронизации работы программы и сопроцессора.

Бит разрешения защиты РЕ (Protection Enable). При РЕ = 1 процессор работает в защищенном режиме; при РЕ = 0 в реальном. РЕ может быть установлен при загрузке регистра CR0 командами lmsw или mov CR0, а сброшен только командой mov CR0.

Регистр CR1 зарезервирован фирмой Intel для последующих моделей процессоров. Регистры CR2 и CR3 служат для поддержки страничного преобразования адреса. Эти два регистра используются вместе. CR2 содержит полный линейный адрес, вызвавший исключительную ситуацию на последней странице, a CR3 – адрес, указывающий базу каталога страницы.

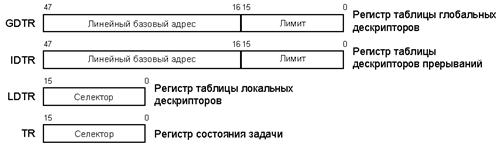

Регистры системных адресов (см. рисунок 1.5) используются в защищенном режиме работы процессора. Они задают расположение системных таблиц, служащих для организации сегментной адресации в защищенном режиме.

Рисунок 1.5 – Регистры системных адресов

В состав процессора входят четыре регистра системных адресов:

GDTR (Global Descriptor Table Register) – регистр таблицы глобальных дескрипторов для хранения линейного базового адреса и границы таблицы глобальных дескрипторов.

IDTR (Interrupt Descriptor Table Register) – регистр таблицы дескрипторов прерываний для хранения линейного базового адреса и границы таблицы дескрипторов прерываний.

LDTR (Local Descriptor Table Register) – регистр таблицы локальных дескрипторов для хранения селектора сегмента таблицы локальных дескрипторов.

TR (Task Register) – регистр состояния задачи для хранения селектора сегмента состояния задачи.

Отладочные регистры и регистры тестирования будут рассмотрены в главе 4.

Рассмотрим пример простой программы для 32-разрядного процессора.

Пример 1.1. Программа сложения 32-разрядных операндов

. 386

2015-04-01

2015-04-01 948

948