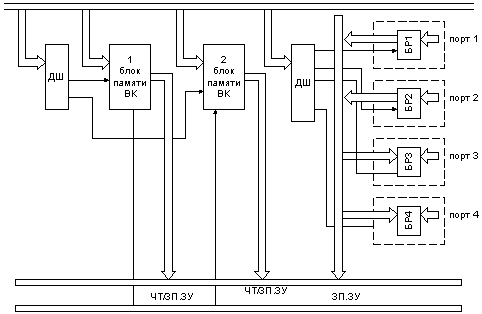

Несмотря на функциональное различие, внутренние интерфейсы используют один и тот же прием выбора адресуемого устройства - декодирование адресного кода. На рис. 4.3 изображена совмещенная функциональная схема внутреннего (для обращения к памяти) и внешнего (для обращения к ВУ) интерфейсов. В обоих случаях дешифратор используется для одинаковой цели - декодировать адресный код на его входе и с помощью активного уровня выходного сигнала обеспечить выбор адресуемого устройства. Различие схем дешифрации определяется разрядностью шины адреса, принципиальной схемой дешифратора и, конечно, адресом устройства.

Объем блока памяти определяется разрядностью его микросхем. Так, если для адресации ячеек памяти требуется К разрядов, то 16-К разрядов 16-разрядной шины адреса могут быть использованы для адресации различных блоков памяти системы. Чаще всего для этой цели используются старшие разряды шины адреса. Выходные сигналы дешифратора подаются на вывод ВК (выбор кристалла) микросхемы памяти.

Структура внешнего интерфейса имеет некоторые отличия. Кроме дешифратора ДШ, интерфейс содержит буферные регистры БР для временного хранения данных. Буферные регистры служат в качестве «ворот», через которые осуществляется обмен данными между МП и ВУ, часто называются портами ввода-вывода. Для организации порта вывода необходим управляющий сигнал, определяющий номер (или адрес) порта, а также системный управляющий сигнал, определяющий направление передачи информации. Как показано на рис. 4.3, на вход буферных регистров поступает управляющий сигнал ЧТ.ВУ, что определяет порт 1 и порт 2 как порты ввода. Напротив, порт 3 и порт 4 являются портами вывода, так как на входе их буферных регистров БРЗ и БР4 подключён управляющий сигнал ЗП.ЗУ. Разрядность буферных регистров может быть согласована с разрядностью шины данных, но может и отличаться от нее. В последнем случае при вводе данных в МП через шину данных программными средствами необходимо очистить неиспользованные разряды.

Рис. 4.3

Если разрядность выходного кода ВУ больше разрядности шины данных, то для формирования слова данных, поступающего из ВУ, также необходимо использовать несколько дополнительных команд. 1

Заметим, что наряду с главной функцией буферного регистра - временное хранение данных - он одновременно используется и как усилитель мощности, что упрощает согласование шины данных микроконтроллер с низкоомным выходом внешнего устройства. В некоторых случаях порты ввода-вывода могут не содержать буферных регистров. Тогда они строятся на основе шинных формирователей, и это необходимо учитывать при разработке программного обеспечения системы.

Алгоритм функционирования интерфейса сводится к следующему. При выполнении команды обращения к ВУ на шине адреса МП выставляет адрес ВУ. Дешифратор дешифрирует адресный код, и соответствующим сигналом с выхода ДШ подготавливаются цепи"; приема данных. В следующем такте команды данные передаются из МП в адресуемый буферный регистр и управляющим сигналом ЗП.ВУ записываются в выбранный БР, после чего они становятся доступны ВУ.

Взаимосвязь микропроцессора и ВУ упрощается благодаря использованию специальных интерфейсных БИС-адаптеров, обеспечивающих различные способы обмена данными.

2015-04-30

2015-04-30 542

542