Лабораторная работа № 5. Цифровые комбинационные устройства

Цифровые комбинационные устройства.

Цифровые комбинационные устройства (КУ) представляют собой логическую схему с m входами (m ³ 1) и n выходами (n ³ 1), у которой состояния выходов, т. е. информационные значения выходных сигналов, в данный момент времени определяются лишь состояниями входов в этот же момент времени. Синтез КУ выполняется на основе правил функционирования КУ, которые могут быть заданы словесно, в виде таблицы истинности, структурной формулой. Далее на основании правил алгебры логики или с помощью специальных методов (карт Карно и т. д.) производится минимизация структурной формулы КУ. Производят, если это необходимо, преобразование минимизированной структурной формулы к форме, содержащей лишь логические операции заданного базиса (И-НЕ, ИЛИ-НЕ). На основании структурной формулы составляют функциональную и принципиальную схемы КУ. Рассмотрим несколько примеров реализации КУ.

a) Комбинационные сумматоры

В целях максимального упрощения работы компьютера все многообразие математических операций в процессоре сводится к сложению двоичных чисел. Поэтому главной частью процессора являются сумматоры, которые как раз и обеспечивают такое сложение.

Полусумматор. Вспомним, что при сложении двоичных чисел в каждом разряде образуется сумма и при этом возможен перенос в старший разряд. Введем обозначения слагаемых (А, В), переноса (Р) и суммы (S). Таблица сложения одноразрядных двоичных чисел с учетом переноса в старший разряд выглядит следующим образом:

| Слагаемые | Перенос | Сумма | |

| А | В | Р | S |

Из этой таблицы видно, что перенос можно реализовать с помощью операции логического умножения:

Р = А&В.

Получим теперь формулу для вычисления суммы. Значения суммы близки к результату операции логического сложения (кроме случая, когда на входы подаются две единицы, а на выходе должен получиться нуль).

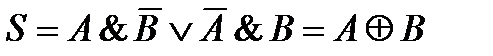

Для определения суммы можно применить следующее логическое выражение:

т. е. полусумматор имеет два выхода (S, P) и реализуется с помощью устройства неравнозначности и схемы И. Функциональная схема полусумматора представлена ниже.

Рис. 10

Два одноразрядных полусумматора образуют одноразрядный сумматор. Сумматор — логическая схема, имеющая три входа (входы разрядов А и В суммируемых чисел и вход С для возможного переноса, образованного при сложении младших разрядов). Сумматор может быть образован с помощью двух полусумматоров и элемента ИЛИ.

Таблица истинности одноразрядного сумматора показана ниже.

| А | В | С | S | P |

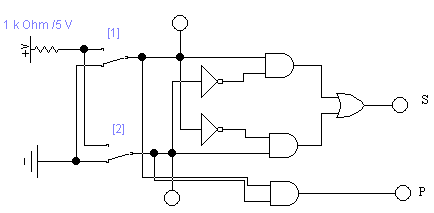

Для построения функциональной схемы одноразрядного сумматора в программе Electronics Workbench имеется схема полного двоичного сумматора

Полный двоичный сумматор производит сложение трех одноразрядных двоичных чисел. Результатом является двухразрядное двоичное число, младший разряд которого назван суммой, старший разряд – переносом.

Полный двоичный сумматор производит сложение трех одноразрядных двоичных чисел. Результатом является двухразрядное двоичное число, младший разряд которого назван суммой, старший разряд – переносом.

Устройство имеет три входа и два выхода. Входы: слагаемых – А, В и переноса – Carry IN. Выходы: суммы – Sum и переноса – Carry OUT. Полный двоичный сумматор можно реализовать на двух полусумматорах и одном элементе ИЛИ.

Функциональная схемаполного двоичного сумматора показана на рис.6.

Рис. 11

2015-05-10

2015-05-10 630

630