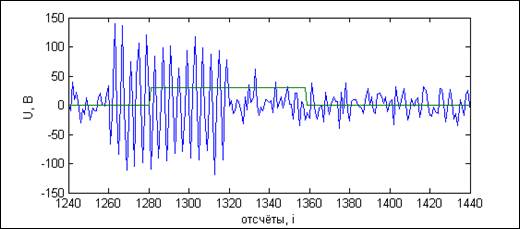

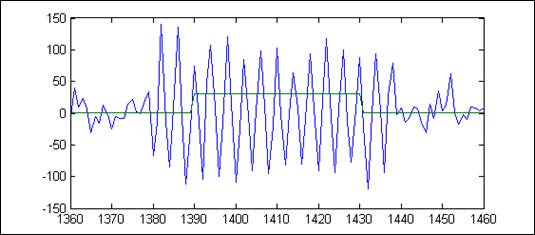

В общем случае сигнал обнаружения не согласован с полезным сигналом.

Рисунок 2.1. – Рассогласование сигнала обнаружения и полезного сигнала

Для формирования измерительного строба необходимо согласовать сигнал обнаружения и полезный сигнал, а также учесть явление Гиббса (искажение сигнала по краям импульса из-за обрезания ИХ фильтра Гильберта).

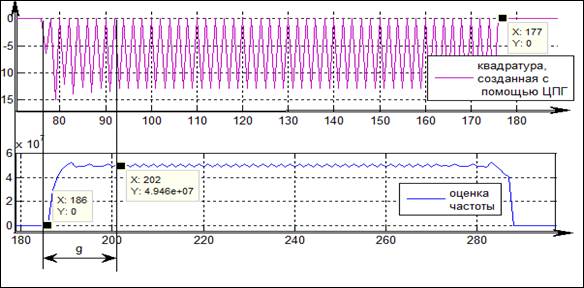

Рисунок 2.2. – явления Гиббса при оценке частоты (см. “Повышение точности измерения параметров сигналов в цифровом тракте” Инженерный вестник, 2014 г. №10, 642-647)

Учитывая то, что при пороге отличным от нуля происходит запаздывание обнаружения сигнала необходимо ввести поправочное число:

, где threshold – порог в момент обнаружения, NoiseAmpl – уровень шумов в момент перед появлением сигнала, Nких – количество отсчётов фильтра, формирующего огибающую (В нашем случае Nких = N32 + N5 = 37), EnvelopeAmpl – амплитуда огибающей (сигнала).

Физический смысл этой формулы следующий: какое количество отсчётов сигнала с амплитудой “EnvelopeAmpl” необходимо занести в фильтр длиной “Nких” чтобы превысить порог с уровнем “threshold”, учитывая то, что начальный уровень (до появления сигнала) огибающей “NoiseAmpl”.

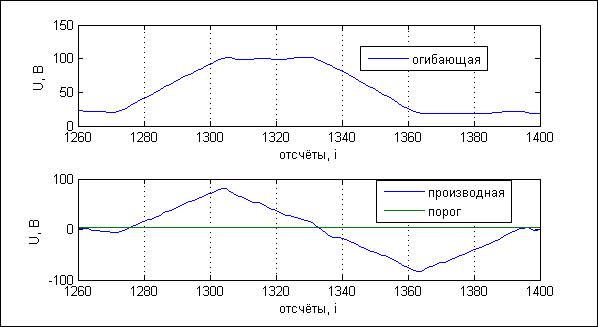

Для того чтобы определить амплитуду огибающей нужно определить момент времени в котором она максимальна, для этого необходимо взять производную от огибающей. Вычисление производной можно производить так: вычислить разность соседних отсчетов и сгладить затем ее КИХ фильтром порядка  , после этого находим точку второго пересечения производной с порогом близким к нулю (с большего в меньшее), и в этот момент назначаем амплитуде значение огибающей задержанное на величину

, после этого находим точку второго пересечения производной с порогом близким к нулю (с большего в меньшее), и в этот момент назначаем амплитуде значение огибающей задержанное на величину  .

.

Рисунок 2.3. – Определение амплитуды сигнала.

Также стоит заметить что в Verilog-моделе в КИХ фильтрах реализован алгоритм конвейерной обработки, которая вносит дополнительные задержки, но обеспечивает необходимую скорость обработки сигнала в реальном времени. Эти задержки также учтены при формирование измерительного строба.

Рисунок 2.4. – Задержанный сигнал и измертиельный строб на выходе Verilog-модели

Рисунок 2.5. – Структурная схема Verilog-модели

2015-05-20

2015-05-20 580

580