Лабораторная работа № 2

Исследование дешифраторов и демультиплексоров

Цель работы: изучение принципов синтеза комбинационных схем (КС) и построения на их основе схем дешифраторов, а также освоение методики их моделирования с помощью пакета прикладных программ MULTISIM и MAX+plusII.

При подготовке к работе необходимо: проработать теоретический материал, выполнить синтез заданной КС, провести экспериментальное исследование схем дешифраторов в соответствии с заданным номером варианта (табл. 2.1), и отмоделировать их на ЭВМ с использованием пакета MULTISIM, а затем собрать заданную схему в MAX+plus II.

Таблица 2.1 Варианты для выполнения индивидуального задания

| № варианта | Полная схема | Схема Россия (зарубежный аналог) | Выполняемая функция | Расширение возможностей DS - DC |

| К561ИД1 (4028/4028BT) | Дешифратор 4®10 с открытым коллектором | Фрагмент на 6 | ||

| К155ИД3 (74154/74154N) | Дешифратор 4®16 Демультиплексор 4®16 | Каскадное соединение 2 ИМС | ||

| К155ИД4 (74155/74LS155D) | Дешифратор 2®8 | Расширение за счет объединения 2 ИМС | ||

| К1564ИД5 (74156/74LS156D) | Дешифратор 2®8 | Расширение за счет управления на 3 ИМС | ||

| К155ИД6 (7442/7442N) | Дешифратор 4®10 | Фрагмент на 7 | ||

| К155ИД7 (74138/74LS138D) | Дешифратор 3®8 | Каскадное соединение 3 ИМС | ||

| К155ИД10 (74145/74LS145D) | Дешифратор 4®10 | Расширение за счет объединения 3 ИМС | ||

| К531ИД14 (74139/74LS139D) | Дешифратор 2®4 | Расширение за счет управления на 2 ИМС | ||

| К561ИД1 (4028/4028BD) | Дешифратор 4®10 | Расширение за счет управления на 2 ИМС | ||

| К155ИД3 (74154/74154N) | Дешифратор 4®16 | Расширение за счет управления на 3 ИМС | ||

| К155ИД4 (74155/74LS155N) | Дешифратор 2®8 | Расширение за счет управления на 2 ИМС | ||

| К1564ИД5 (74156/74LS156N) | Дешифратор 2®8 | Фрагмент на 6 | ||

| К155ИД6 (7442/7442N) | Дешифратор 4®10 | Фрагмент на 8 | ||

| К155ИД7 (74138/74LS138N) | Дешифратор 3®8 | Расширение за счет объединения 3 ИМС | ||

| К155ИД10 (74145/74LS145N) | Дешифратор 4®10 | Расширение за счет управления на ИМС | ||

| КР531ИД14 (74139/74LS139N) | Дешифратор 2®4 | Каскадное соединение 2 ИМС |

Примечание: цифры в строке “полная схема” соответствуют построению полных дешифраторов 2-х, 3-х, 4-х разрядных двоичных кодов, где n=2,3,4-количество входов у дешифратора; в строке “фрагмент” - фрагментам схем дешифраторов 6-ти, 7-ми, 8-ми, 9-ти, 10-ти разрядных двоичных кодов с шестнадцатью выводами позиционного пространственного кода, где n=6,7,8,9,10-количество входов у дешифратора.

Дешифраторы являются преобразователями кодов, выполняющими преобразование двоичного или двоично-десятичного кода в унитарный код (код, представленный 2n разрядами для двоичного n-разрядного числа, только один из разрядов которого равен “1”).

Полным дешифратором с прямыми выходами (DC-Decoder) называется КС, имеющая n входов и реализующая 2n минтерма:

Fi = ki(v) =  , (2.1)

, (2.1)

где v = (xn,…,x1), i = en…e1-двоичное число, а i = 0,1,2…2n - 1-десятичное число; если ep=1, то xp = x, если ep = 0, то xp=  .

.

Такие дешифраторы называются дешифраторами n x 2n. В соответствии со свойствами минтермов при каждой комбинации значений входных сигналов xp только один выход Fi принимает значение, равное 1. Поэтому дешифраторы широко используются в коммутаторах электронных устройств, обеспечивая включение в каждый момент времени только одного устройства.

Дешифраторы различают по ёмкости (2, 3, 4 бита), по числу каналов (один или два), а также форматом входного кода (двоичный или двоично-десятичный). Дешифраторы могут быть как полными, так и неполными.

Неполным дешифратором называется КС, имеющая n входов, но реализующая N<2n минтермов n переменных. Такие дешифраторы называются дешифраторами n x N. В виде ИС выпускаются дешифраторы 4 x 10, 4 х 7 и другие.

Полным дешифратором называется комбинационная схема (КС), имеющая n входов и 2n выходов и реализующая на выходах с номерами 0,1,2…2n-1 значения булевых функций соответственно:

K0=`Xn`Xn-1…`X2`X1;

K1=`Xn`Xn-1…`X2 X1;

K2=`Xn`Xn-1… X2`X1; (2.2)

…………………………

Kn-1 = Xn Xn-1… X2 X1;

Например, дешифратор 2´4 имеет 2 входа и 4 выхода, на которых реализованы функции K0, K1, K2, K3.

Принципиальная схема этого дешифратора приведена на рис. 2.1а.

Рис. 2.1 Дешифратор 2 ´ 4: а) принципиальная схема; б) условное обозначение

Дешифратор может быть неполным, реализующим m<2n функций (пример использования: преобразование двоично-десятичного кода в код, предназначенный для управления десятичным индикатором - дешифратор 4´10).

На основе полных дешифраторов строят дешифраторы - демультиплексоры выполняющие функции ¦i = V×Ki×(Xn…X1), то есть используется дополнительный вход V, сигнал с которого подаётся на все логические элементы полного дешифратора (рис. 2.2).

Рис. 2.2 Четырёхканальный дешифратор-демультиплексор.

Принципиальная схема ИМС К155ИД4 приведена на рис. 2.3.

Рис. 2.3 Принципиальная схема сдвоенного 4-х канального дешифратора-демультиплексора (ИМС К155ИД4), где D 1, D 2- адресные входы; V 1, V 2 и V 3, V 4- стробирующие; A0 -A3 и B0 -B3 – выходы (по 4 на каждый дешифратор)

Дешифратор выполняет следующие функции:

(2.3)

(2.3)

где j = 0, 1, 2, 3;

при  и

и  получается сдвоенный дешифратор 2´4 с инверсными выходами (рис. 2.4).

получается сдвоенный дешифратор 2´4 с инверсными выходами (рис. 2.4).

а) б)

Рис. 2.4 Сдвоенный 4-х канальный дешифратор-демультиплексор (ИМС К155 ИД4): а) функциональная схема; б) условное графическое обозначение

Сдвоенный демультиплексор с одного входа на 4 выхода получают, если входы V2 и V4 используют для передачи данных соответственно для первого и второго демультиплексоров, входы V1 и V3 - стробирующие, а общие входы D1 и D2 используются для выбора (подключения) необходимого выхода.

Если положить V2 =`V4 = D3 и`V1 =`V3 º 0, то получится 8-ми канальный дешифратор-демультиплексор, выполняющий функции:

и

и

Рис. 2.5 Восьмиканальный дешифратор-демультиплексор, выполненный на ИМС К155 ИД4. Функциональная схема

При`Vº0 данная схема представляет собой дешифратор 3´8 с инверсными выходами.

16-ти канальный дешифратор-демультиплексор реализован на ИМС К155 ИД3 (рис. 2.6).

Рис. 2.6 Принципиальная схема ИМС К155ИД3.

16-канальный дешифратор-демультиплексор

Вышеупомянутая ИМС К155ИД3 выполняет функцию:

(2.4)

(2.4)

- это коммутатор, который передаёт сигнал  на один из 16-ти выходов в зависимости от значений сигналов на 4-х адресных входах (рис. 2.7).

на один из 16-ти выходов в зависимости от значений сигналов на 4-х адресных входах (рис. 2.7).

Рис. 2.7 Условное графическое обозначение16-ти канального дешифратора-демультиплексора ИМС К155 ИД3

Условное обозначение

Если положить`V1 =`V2 º 0 ИМС выполняет функцию дешифратора 4´16 с инверсными выходами.

Использование двух дополнительных входов`V1 и`V2 позволяет построить 32-х канальный дешифратор-демультиплексор (рис. 2.8).

Рис. 2.8 32-х канальный дешифратор-демультиплексор, выполненный на 2-х ИМС К155 ИД3. Функциональная схема

V2 используется в качестве 5-го адресного входа, имеющего вес - 16, а на вход`V1 подаётся коммутирующий на 32 выхода сигнал`V, т.е. схема выполняет функции:

; (2.5)

; (2.5)

принимая`Vº0 получаем дешифратор 5´32 и инверсными выходами.

Из логических элементов, являющихся дешифраторами, можно строить дешифраторы на большее число входов. При этом, как правило, используются дешифраторы с инверсными входами синхронизации. Каскадное включение таких схем позволяет легко наращивать число дешифрируемых переменных. Принцип построения схем нетрудно понять, обратившись к рис. 2.9. Здесь показан дешифратор на 4 входа с инверсными выходами, построенный из интегральных элементов, реализующих схемы двухвходовых дешифраторов.

Рис. 2.9 Каскадный дешифратор. Функциональная схема на 4 входа и 16 выходов

Таким образом, имея в виду всё выше сказанное, можно построить любой фрагмент заданных схем дешифраторов.

Рис. 2.10 Фрагмент функциональной схемы дешифратора 6х64

Указания по моделированию дешифраторов на ЭВМ с использованием пакета программ MULTISIM

С помощью ЭВМ необходимо смоделировать схемы дешифраторов согласно Вашему варианту. Далее показан пример: дешифратор, который задаёт дешифрацию двоичного кода в коды управления семисегментным индикатором.

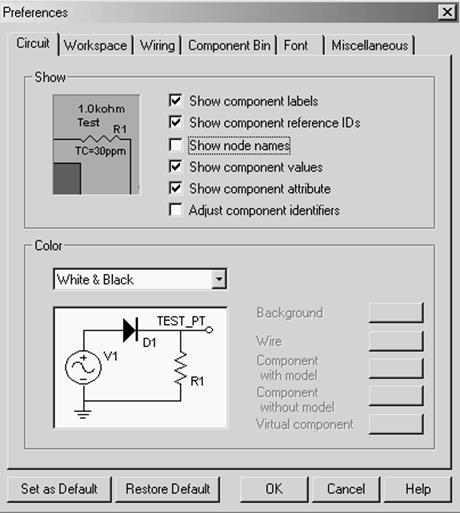

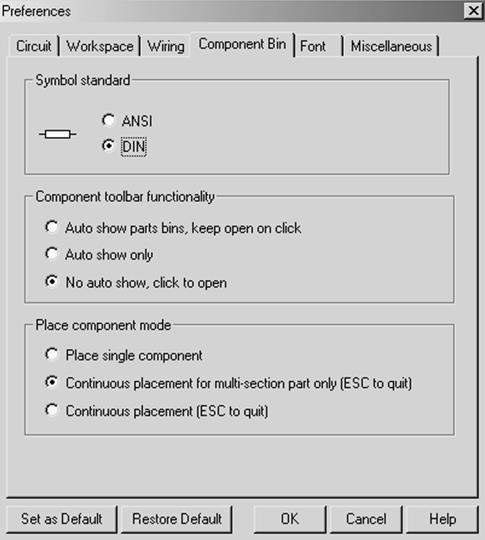

1. Запустите пакет программ Multisim. В меню Options нажмите Preferences для настройки Вашего рабочего места. В свойстве Color можно выбрать подходящие для Вас цвета (рис. 2.11), а в закладке Component Bin в стандарте символов установите DIN. Нажмите ОК..

Рис. 2.11 Выбор цветовой схемы

Рис. 2.12 Выбор стандарта для отображения элементов

2. Соберите схему дешифратора в соответствии с вариантом в таблице, используя линейку инструментов и панель инструментов (см. руководство пользователя Multisim).

3. Подключите генератор сигналов и логический анализатор (или несколько) к собранному дешифратору. Пример подключения показан на рис. 2.13.

|

Рис. 2.13 Дешифратор, для преобразования двоичного кода в коды управления семисегментным индикатором

Рис. 2.13 Дешифратор, для преобразования двоичного кода в коды управления семисегментным индикатором

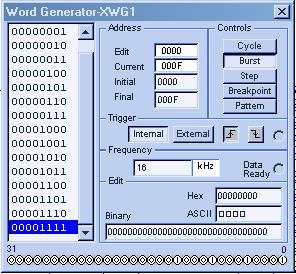

4. Установите необходимые последовательности сигналов на выходе генератора. Установите значение параметра Frequency (рекомендуемое 16 кГц).

Рис. 2.14 Входные сигналы

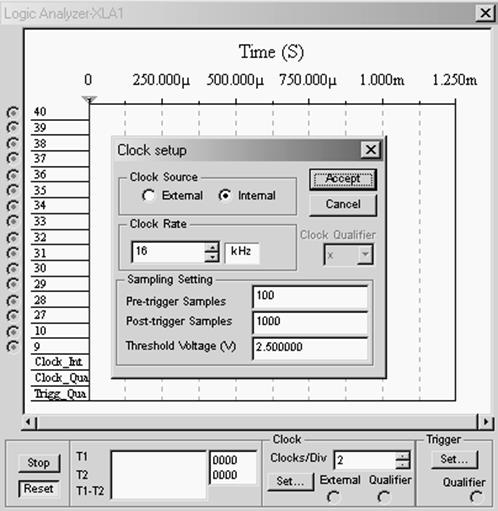

5. В настройках Clock Setup логического анализатора (если несколько, то всех) установите значение частоты, равное значению, выбранному в генераторе слов (это важно, особенно при внутренней синхронизации логического анализатора).

Рис. 2.15 Задание частоты следования сигналов

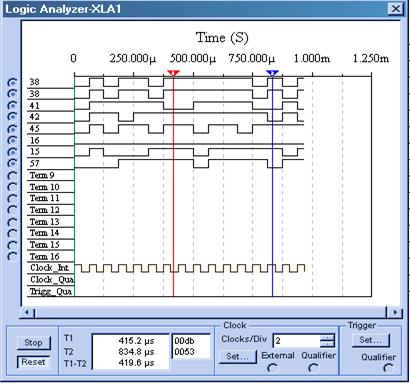

6. Активизируйте анализатор сигналов и включите схему (Кнопка ВКЛ / ВЫКЛ схемы, обычно справа вверху).

7. Пронаблюдайте и зафиксируйте сигналы на выходе.

Рис. 2.16 Сигналы на выходе

2.3 Порядок проведения работы с использованием пакета MAX+PLUS

1. Процедура разработки нового проекта.

Процедуру разработки нового проекта можно упрощённо представить следующим образом:

1.1 Запуск пакета осуществляется щелчком по иконке  .

.

1.2 Создание нового файла проекта или иерархической структуры нескольких файлов проекта с помощью любого сочетания редакторов в системе MAX+PLUS II, то есть графического, текстового и сигнального редакторов. Для этого выбираем из меню File / New.

|

Текстовый редактор

Сигнальный редактор

Рис. 2.17 Окно создания нового файла

Выбираем графический редактор, щелкая по кнопке Graphic Editor file. В результате на экране появиться окно программы с чистым окном редактирования схемы.

Рис. 2.18 Общий вид программы

1.3 Задание имени файла проекта верхнего уровня в качестве имени проекта. Для этого выбираем из меню: File / Project / Name.

|

задание имени файла

проекта верхнего уровня

Файлы, находящиеся

в папке проекта

Папка, в которой

находиться проект

Рис. 2.19 Задание имени нового проекта

В поле Project Name вводим имя проекта, для нашего примера это sum2 (сумма по модулю 2).

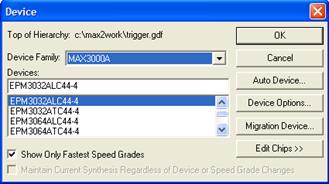

1.4 Назначаем семейство ПЛИС для проекта (например МАХ3000А);

Меню Assign / Device.

Рис. 2.20 Выбор семейства ПЛИС

В поле Device Family выбирается семейство ПЛИС, в данном случае мы выбираем MAX3000А, для удобства проектирования и создания входных сигналов, т.к. данная серия способна воспринимать сигналы с наносекундной задержкой, т.е. те, которые создаются редактором сигналов по умолчанию.

В поле Device выбираем конкретную модель микросхемы. Для данной лабораторной работы выбор какой-то конкретной микросхемы большого значения не имеет, т.к. проектируемые схемы просты и главной задачей работы является освоение пакета, а не проектирование сложной ИС.

2. Создание схемы.

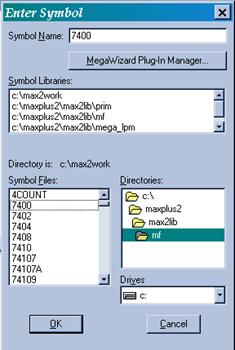

2.1 Для размещения элементов щелкаем по правой кнопке мыши, для появления контекстного меню, в котором выбираем Enter Symbol.

Рис. 2.21 Вставка элемента

2.2 В поле Symbol Libraries два раза щелкаем на строке c:\maxplus2\max2lib\mf, тогда в поле Symbol Files отобразится список элементов данной библиотеки, среди которых надо выбрать необходимые и нажать OK.

Стандартные логические элементы находятся в библиотеке mf.

Входные и выходные элементы находятся в библиотеке prim и называются input и output соответственно. С помощью мышки разместить элементы схемы в окне.

Элемент отрицания находится в библиотеке prim и называется not.

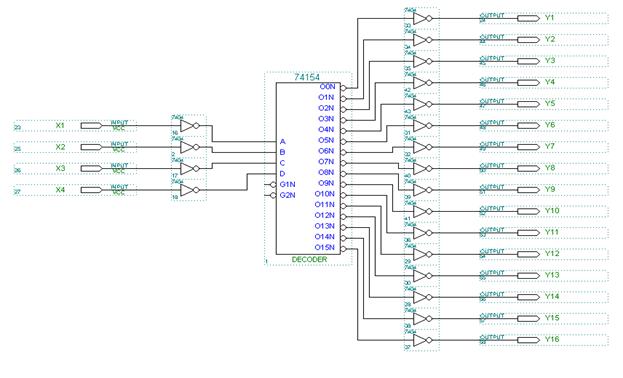

Например, мы строим 32-х канальный дешифратор-демультиплексор, выполненный на 2-х ИМС 74154.

2.3 Далее нажав кнопку  , графическим курсором строим логическую схему.

, графическим курсором строим логическую схему.

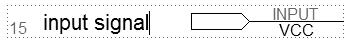

2.4 Теперь зададим имена входных и выходных сигналов.

Для этого щелкаем два раза левой кнопкой мыши по месту, где написано input signal и пишем нужное название. Аналогично для выходных сигналов.

Например, входы обозначаем x1, x2, x3,x4, а выходы – от y (1-16).

В итоге получаем:

Рис. 2.22 Дешифратор, который задаёт дешифрацию двоичного десятичного кода в унитарный код

3. Создание файла.

Файл создается с входными и выходными сигналами.

3.1 Для этого: File/ New/ Waveform Editor File.

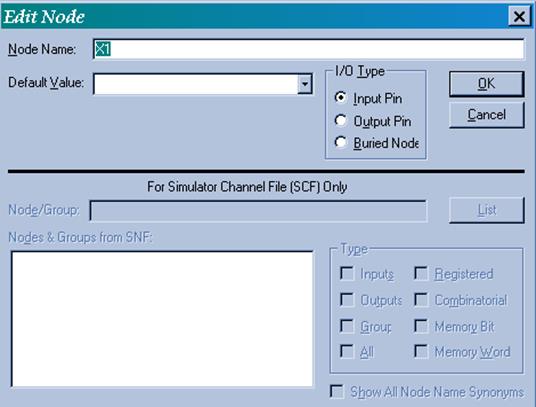

3.2 В появившемся окне двойной щелчок по строке вызывает появление контекстного меню.

Рис. 2.23 Задание имён входных и выходных сигналов

Здесь задаем название сигнала в поле Node Name и его характер в поле I/O Type: входной (input pin), выходной (output pin) или биполярный (buried node). Они должны соответствовать названиям на схеме.

3.3 После этого необходимо задать сами входные сигналы. Строка разделена на дискретные интервалы времени, которые располагаются последовательно. В соответствии с нужной последовательностью выделяем один или несколько интервалов и жмем одну из двух кнопок:

- для низкого уровня,

- для низкого уровня,

- для высокого уровня.

- для высокого уровня.

В меню View / Time Range можно задать видимую на экране часть временных диаграмм.

В меню File / End Time задаем конечное время.

Получаем:

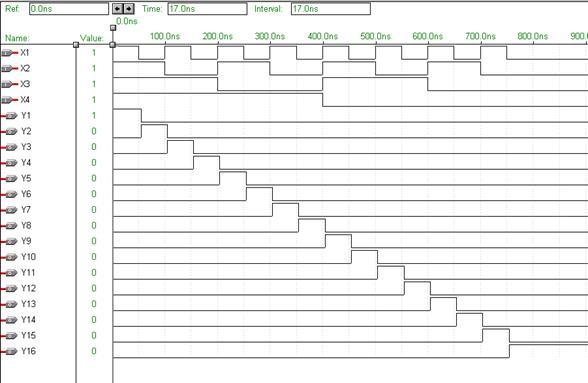

Рис. 2.24 Диаграмма входных и выходных сигналов

4. Компилятор

Предоставляет очень широкие возможности управления алгоритмом компиляции посредством опций меню. В этой работе рассмотрим лишь некоторые возможности (подробнее об этом можно прочитать в руководстве пользователя):

· автоматический или ручной выбор ПЛИС;

· автоматическое разбиение (при необходимости) на несколько корпусов ПЛИС;

· возможность назначения сигналов на конкретные выводы микросхемы;

· возможность размещения конкретных функций в конкретных ресурсах микросхемы;

· оптимизация алгоритмов синтеза;

· временной синтез (с учетом требуемых временных параметров);

· возможность управления соотношением потребление/ быстродействие;

· удобная система отслеживания синтаксических и семантических ошибок.

Открытие окна компилятора Compiler ( ) и выбор кнопки Start для начала компиляции проекта. По желанию пользователя можно подключить модуль извлечения временных параметров проекта Timing SNF Extractor для создания файла, используемого при временном моделировании.

) и выбор кнопки Start для начала компиляции проекта. По желанию пользователя можно подключить модуль извлечения временных параметров проекта Timing SNF Extractor для создания файла, используемого при временном моделировании.

|

Рис. 2.25 Окно компилятора

Все операции симуляции, анализ задержек, размещение элементов на микросхеме выполняются только после компиляции и проверки ошибок, которая осуществляется во время компиляции.

Отображают как логику функционирования, так и реальные временные соотношения сигналов, гонки (состязания). Моделирование осуществляется с высокой степенью адекватности, что существенно упрощает процесс отладки устройства. В случае успешной компиляции возможен временной анализ, для чего следует выполнить следующее:

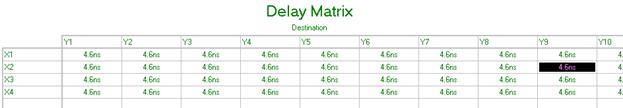

5.1 Для проведения временного анализа задержек открыть окно Timing Analyzer, выбрать режим анализа и нажать кнопку Start.

Рис. 2.26 Анализ временных задержек

По строкам отображается информация о входных сигналах, в столбце о выходном. Таблица представляет собой перекрестную таблицу, показывающую время, через которое сигнал, поданный на вход вызовет реакцию на выходе (например, в нашем случае 7,5ns - задержка сигнал на выходе относительно входа).

|

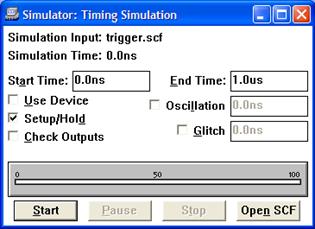

5.2 Для проведения симуляции мы уже создали векторный тестовый вектор в файле канала тестирования (.scf), пользуясь сигнальным редактором. Затем открываем окно отладчика Simulator (иконка

).

). Рис. 2.27 Окно симулятора

Задаем начальное и конечное время и нажимаем Start.

Для просмотра результатов нажимаем Open SCF.

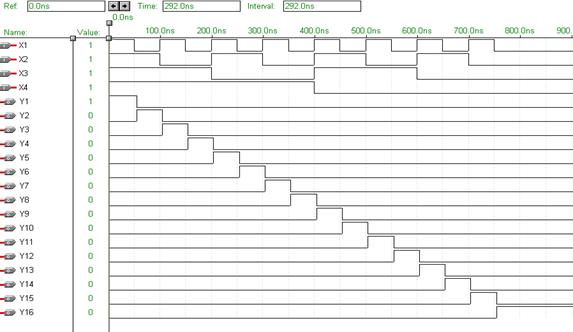

Рис. 2.28 Временные диаграммы

Здесь мы видим значения сигналов на выходах схемы.

2015-05-10

2015-05-10 13789

13789