Цели работы и содержание отчета

Цели работы: 1) Ознакомиться с процессом разработки проекта, включающего в свой состав Soft-процессор на примере MicroBlaze.

2) Ознакомиться с процессом создания файла конфигурации ПЛИС и инструментами, позволяющими проводить отладку проекта для ПЛИС

Отчет

В ходе данной лабораторной работы был рассмотрен возможный путь проектирования системы на кристалле на базе Soft-процессора ПЛИС фирмы Xilinx. В качестве примера рассматривается система на базе процессора MicroBlaze, включающая в себя пользовательский модуль UART, связанный с процессором с помощью интерфейса AXI4-Lite. Данный пример демонстрирует некоторые возможности среды разработки Xilinx Design Tools для создания, моделирования и отладки пользовательских IP ядер и их использования в качестве периферии в микропроцессорной системе.

Путь проектирования такой системы в рассматриваемом примере можно разбить на следующие этапы:

1) Описание работы модуля UART на языке Verilog, его моделирование и отладка (этот этап проделан в Лабораторной работе №1)

2) Параметризация разработанного модуля и оформление его в качестве IP ядра для использования в процессорной системе, работающей на шине AXI (этот этап проделан в лабораторной работе №2)

3) Включение разработанного IP ядра модуля UART в состав системы на базе процессора MicroBlaze с помощью интерфейса AXI4-Lite, с использованием инструментов Xilinx EDK

4) Моделирование работы спроектированной системы с помощью внешней среды Modelsim SE

5) Аппаратная отладка разработанной системы с помощью логического анализатора ChipScope Analyzer

6) Отладка программного обеспечения с помощью инструментов Xilinx SDK

Первые два этапа проделаны в предыдущих лабораторных работах. Поэтому целесообразно начать отчет с этапа №3.

Включение разработанного IP ядра модуля UART в состав системы на базе процессора MicroBlaze с помощью интерфейса AXI4-Lite, с использованием инструментов Xilinx EDK

Выходные результаты, полученные на предыдущих этапах:

1) Отлаженный модуль UART;

2) Параметризованный модуль UART, оформленный в виде IP ядра;

3) Созданный проект в утилите пакета EDK Xilinx Platform Studio (lab_microblaze.xps)

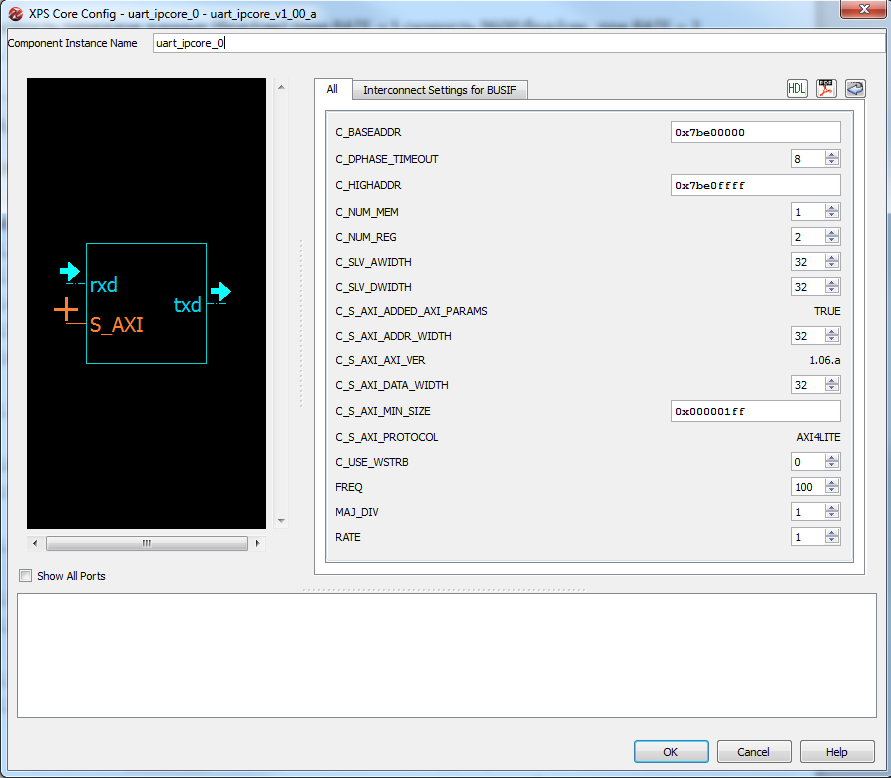

Параметры модуля UART:

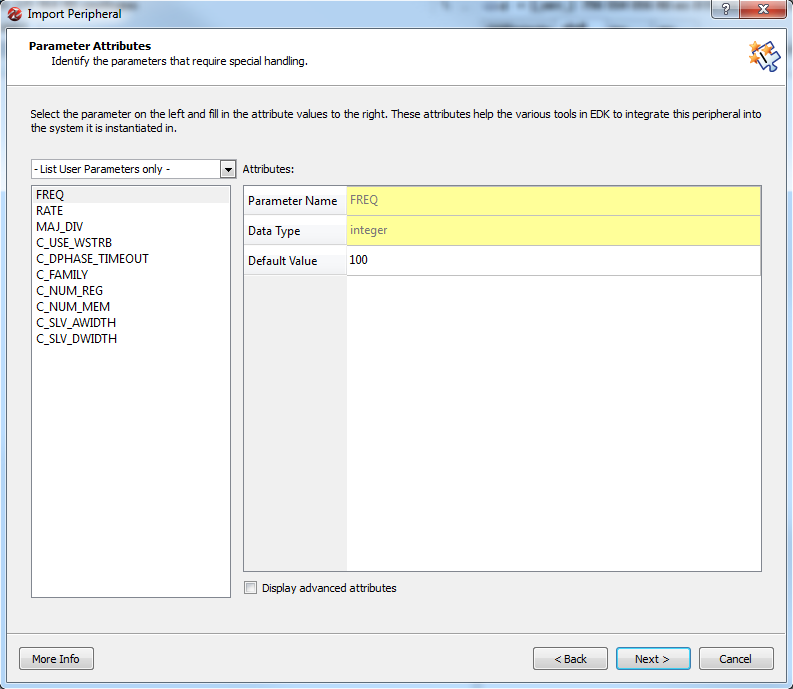

FREQ – тактовая частота, на которой работает модуль (в мегагерцах);

RATE – скорость передачи данных [бод/сек] (при RATE = 1 скорость 9600 бод/сек, при RATE = 2 скорость 19200 бод/сек, при RATE = 12 скорость 115200 бод/сек);

MAJ_DIV – коэффициент разбиения выборки мажоритарной схемы (при MAJ_DIV = 1 выборка из 64 значений, при MAJ_DIV = 2 выборка из 128 значений и т.д.)

1.1. Обновление IP ядра UART с поддержкой slave-интерфейса AXI4-Lite

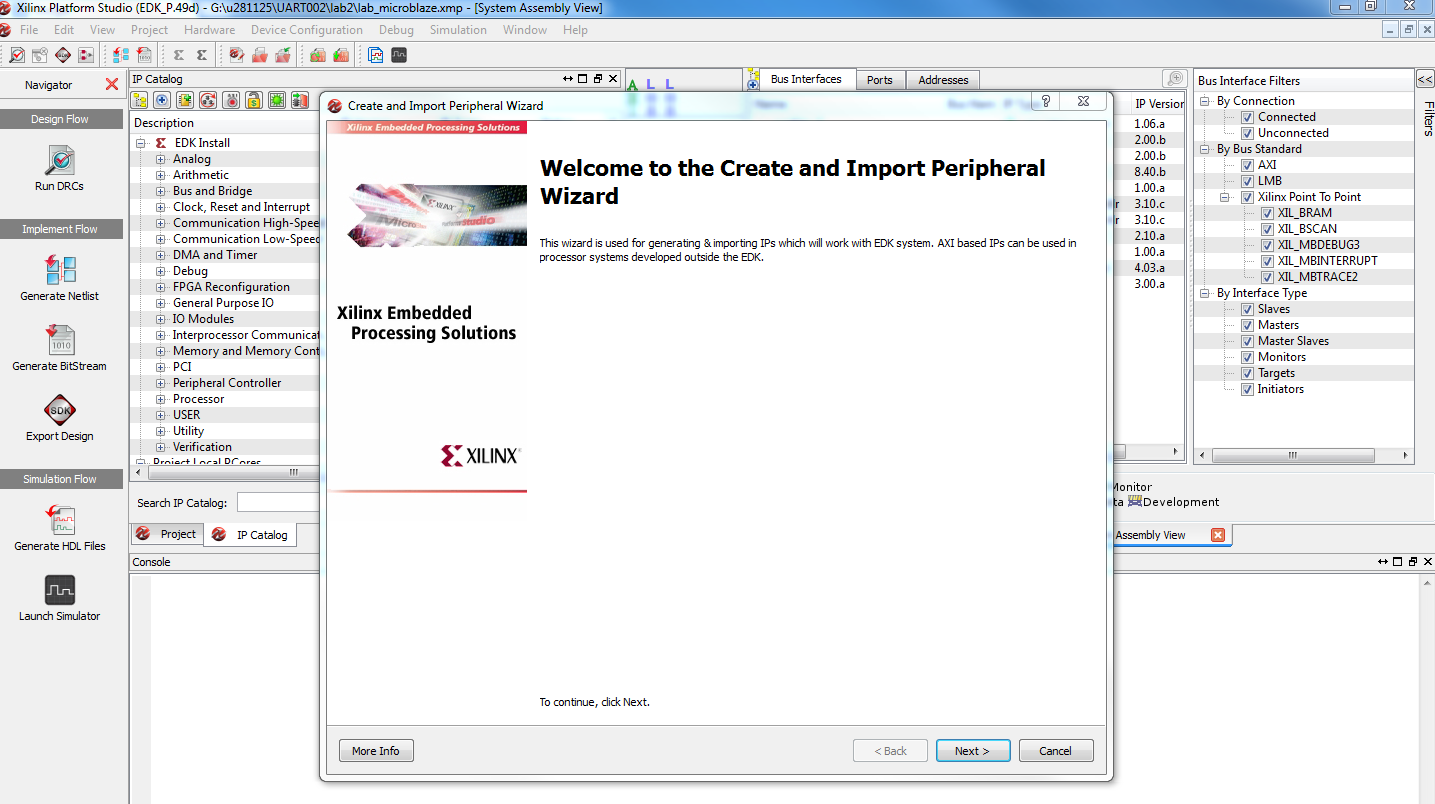

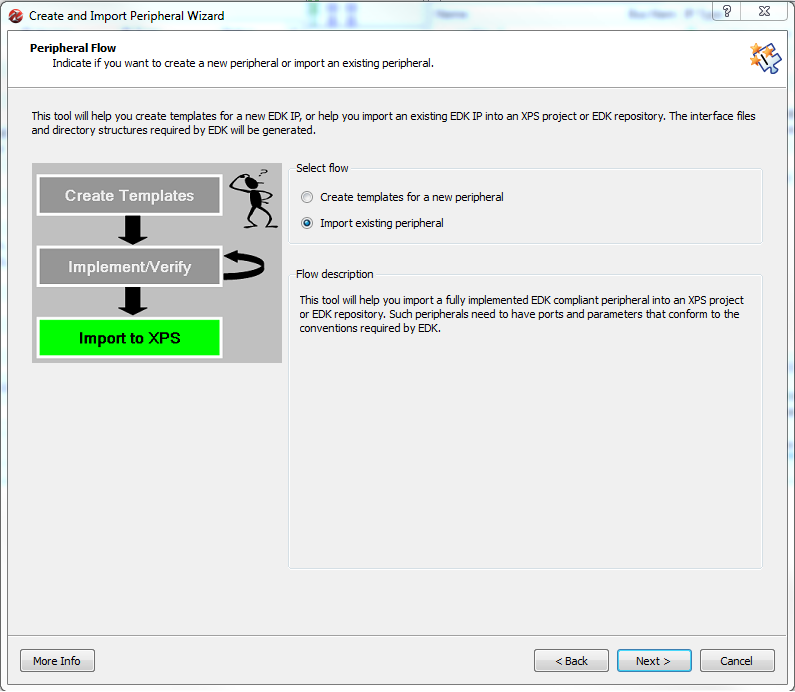

1.1.1 Открыть созданный ранее проект в XPS, далее Hardware -> Create or Import peripheral, Next

1.1.2. Выбрать Import existing peripheral, Next

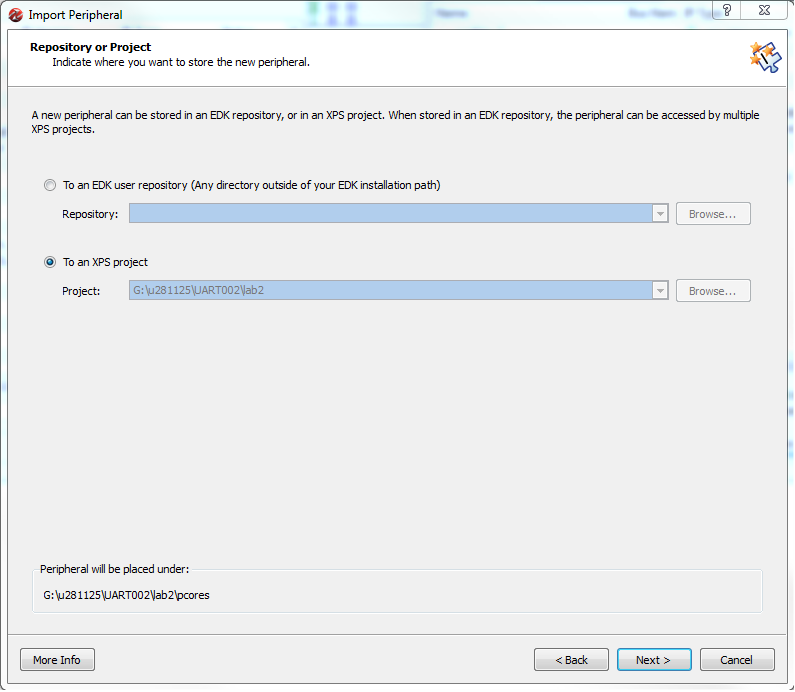

1.1.2 Выбрать To an XPS project, Next

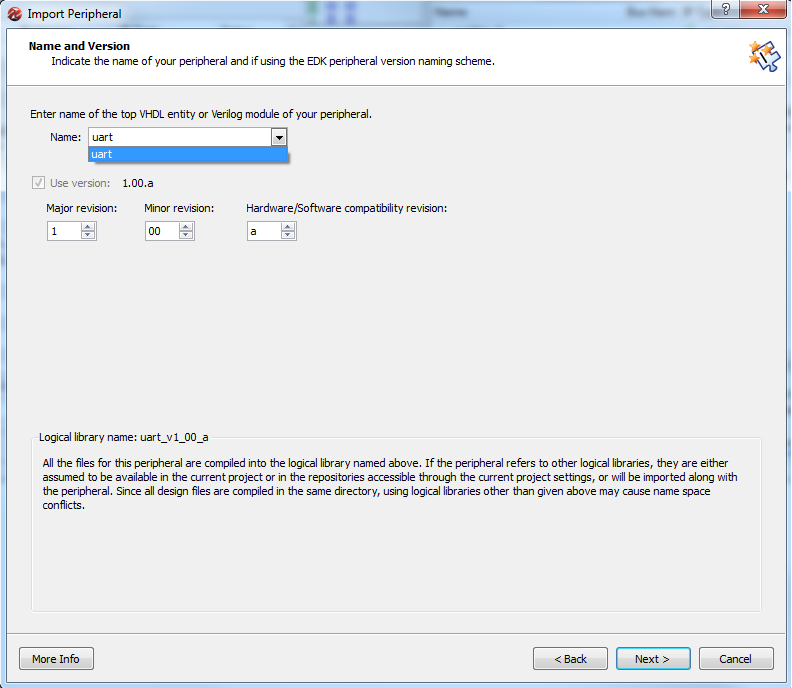

1.1.3. В поле “name” выбрать из выпадающего списка имя разработанного IP ядра UART, Next

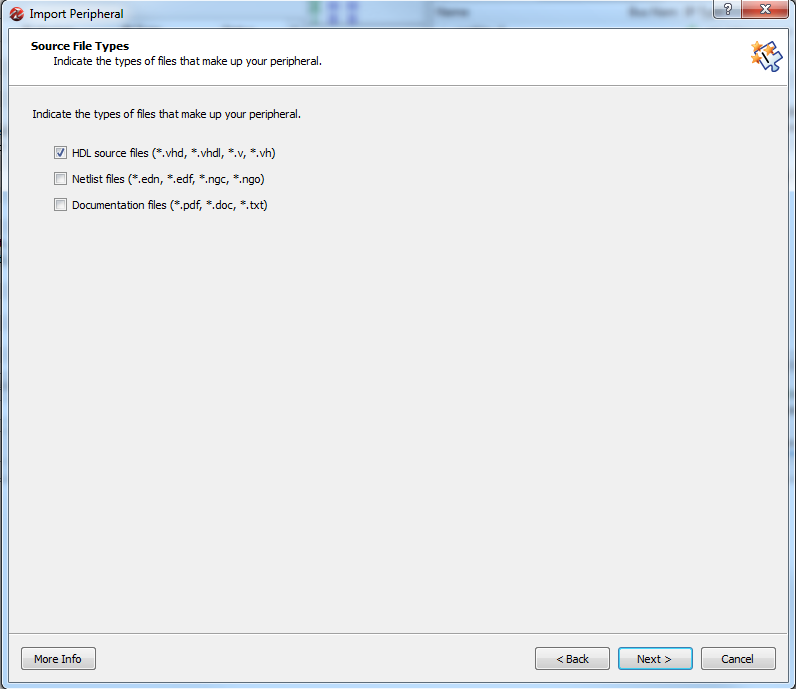

1.1.4. Выбрать HDL source files, Next

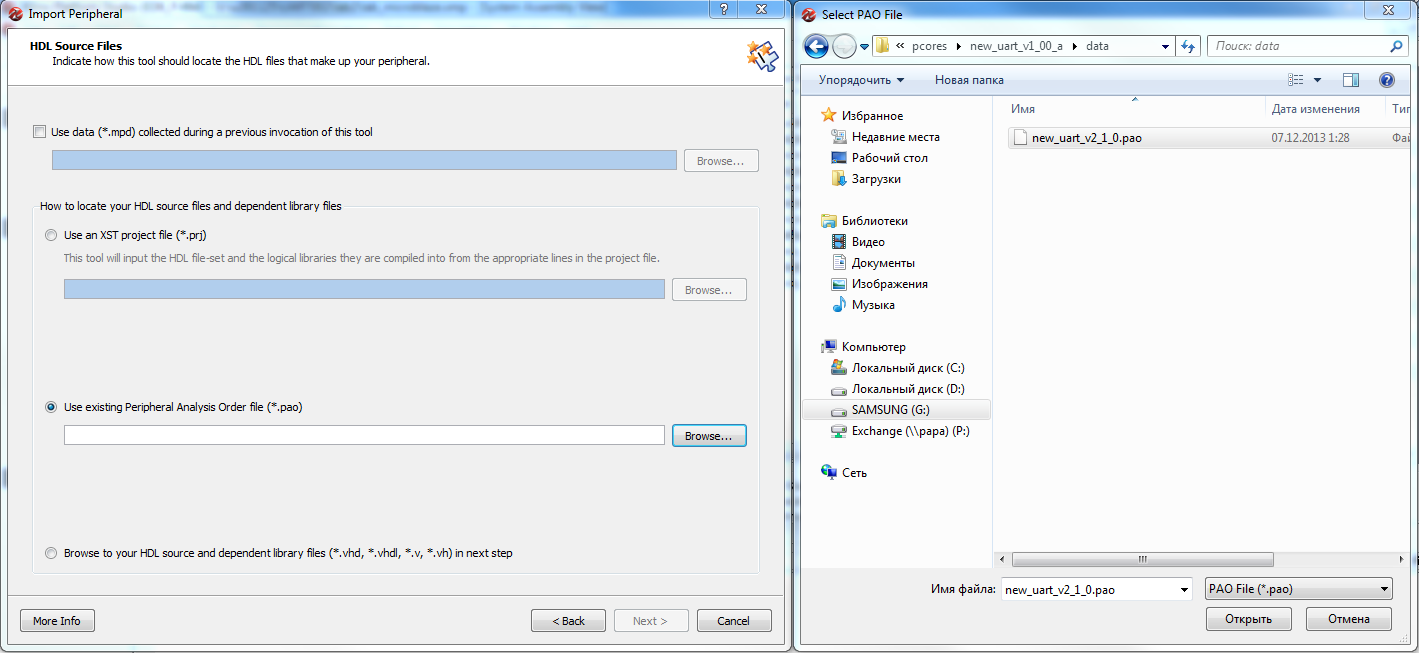

1.1.5. Выбрать “Use existing Peripheral Analysis Order file (*.pao)”, выбрать файл *.pao, расположенный в директории <XPS_project>\pcores\<IP_core>\data, Next

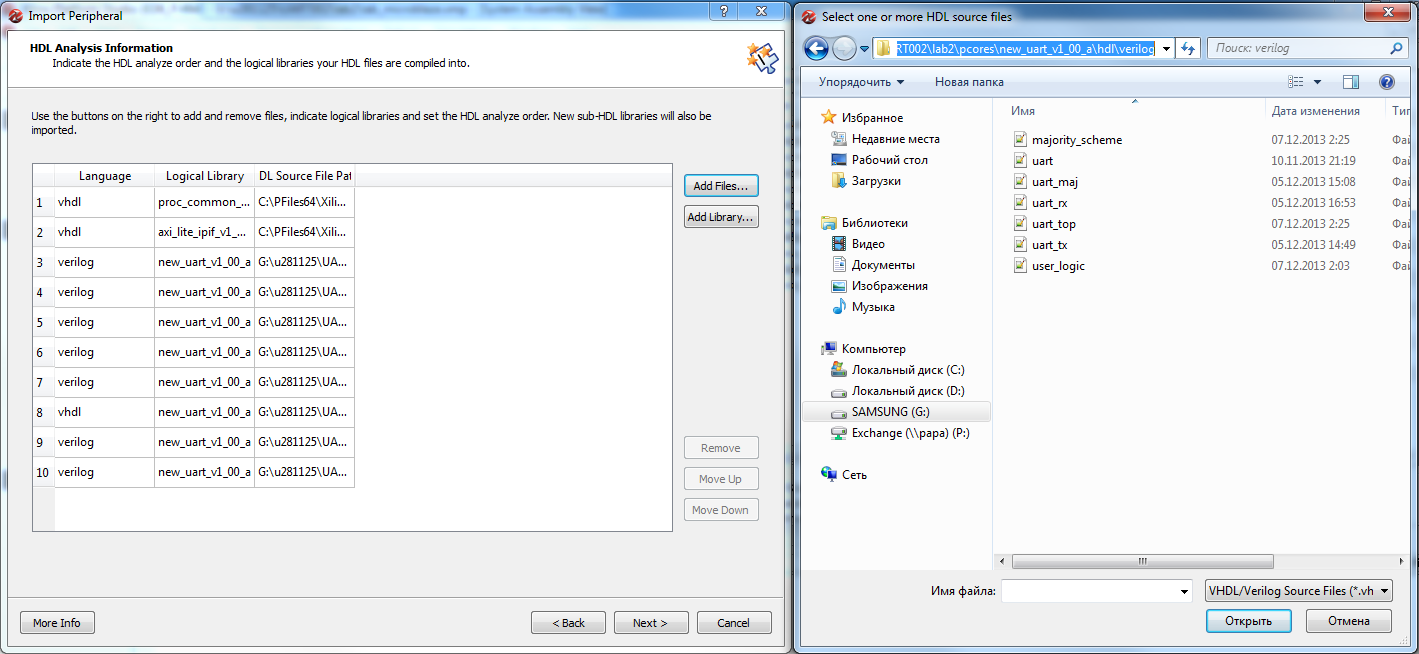

1.1.6. Файлы описания модуля UART на языке Verilog, которые находятся в директории <XPS_project>\pcores\<IP_core>\hdl\verilog, Next

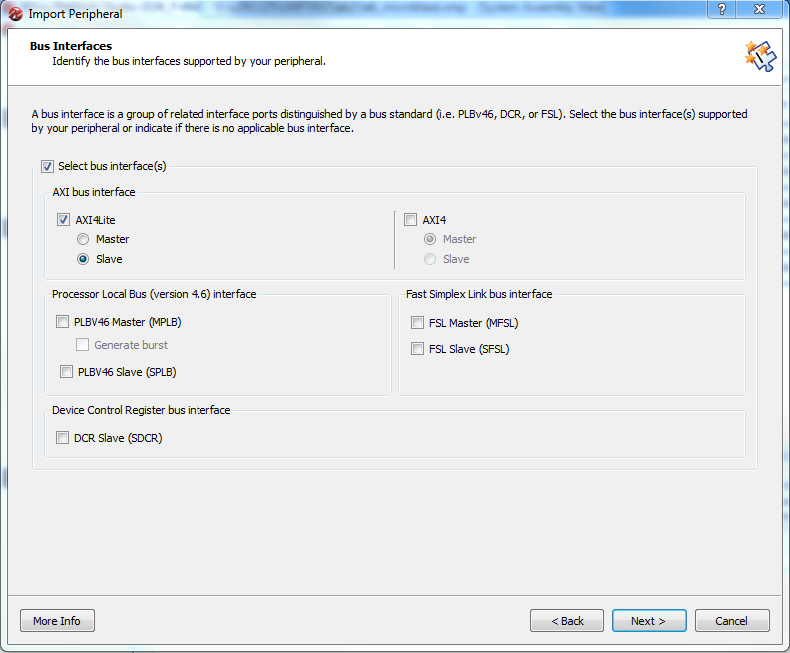

1.1.7. Выбрать в поле “Select bus interface(s)” AXI4Lite (Slave), Next

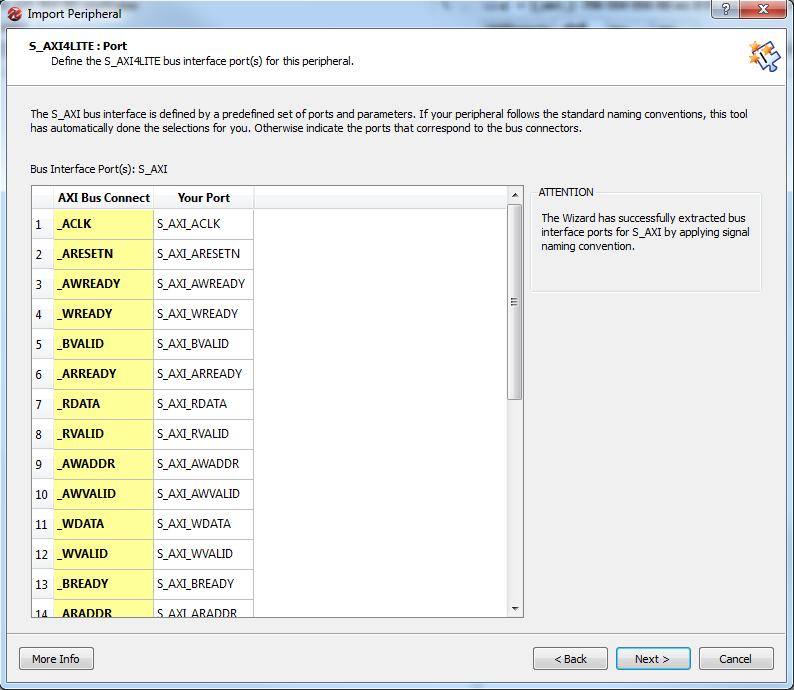

1.1.8. Убедиться, что внешние сигналы IP ядра slave-интерфейса AXI4-Lite соответствуют подключены правильно к общей шине AXI, Next

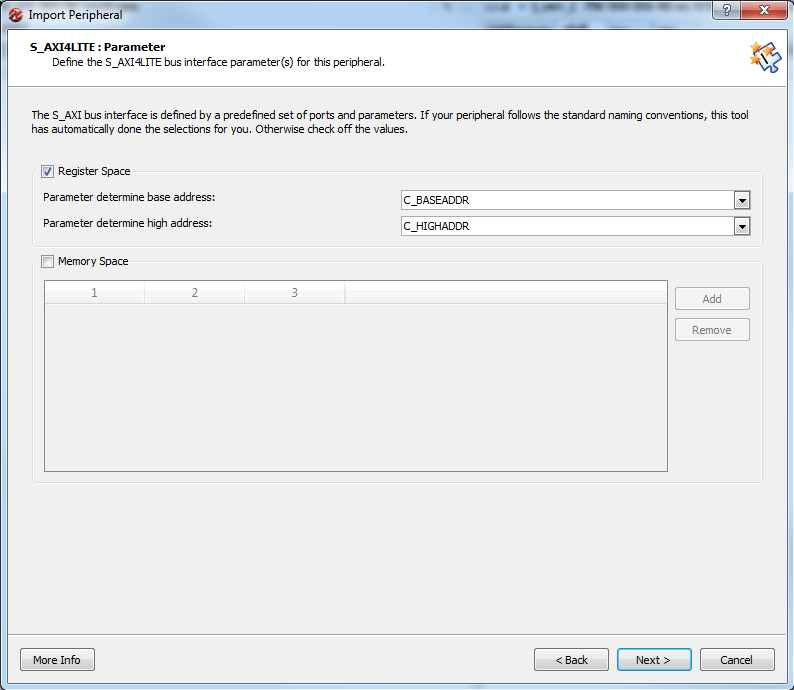

1.1.9. Установить “Parameter determine base address” в значение C_BASEADDR, “Parameter determine base address” в C_HIGHADDR, Next

1.1.10. Установить значение параметров IP ядра, Next

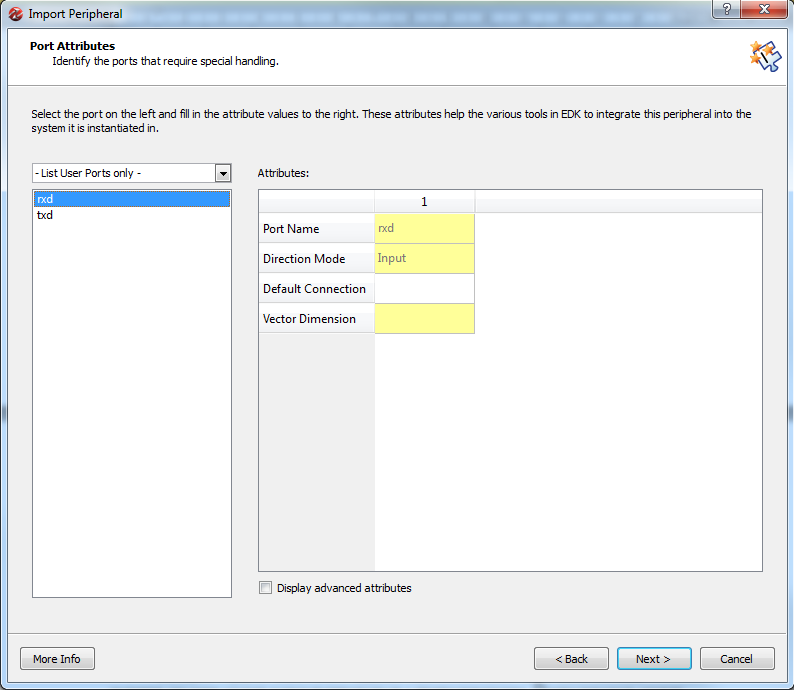

1.1.11. Убедиться в наличии пользовательских сигналов rxd и txd в списке внешних портов IP ядра, Next

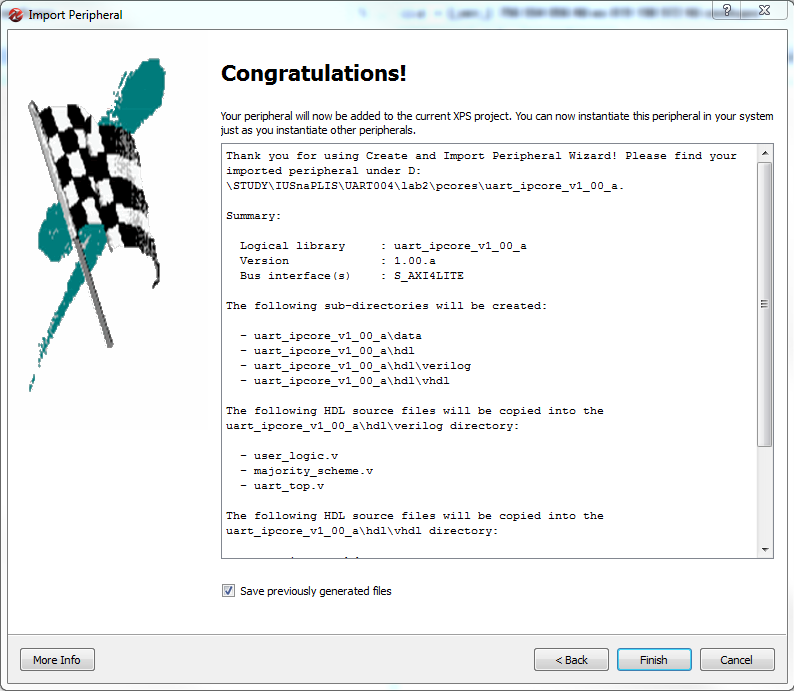

1.1.12. Finish, IP ядро UART готово для подключения в систему

1.2. Подключение IP ядра UART к системе на базе процессора Microblaze в XPS

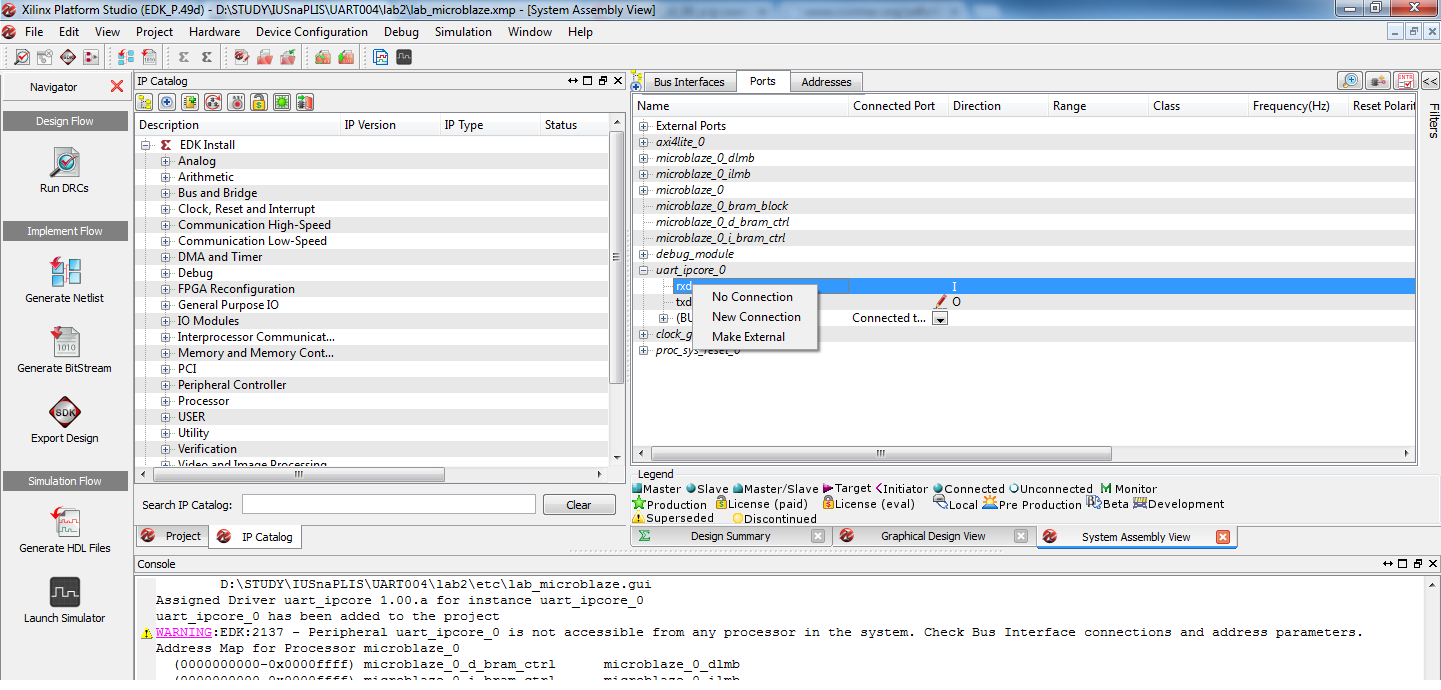

1.2.1. Теперь необходимо вернуться в проект в XPS. В дереве IP catalog -> Project Local Pcores появилось IP ядро IP ядро UART. Для добавления его в систему на базе процессора Microblaze необходимо выполнить следующее: ПКМ -> Add core, установить значения параметров по умолчанию и назначить область адресного пространства для адресуемых регистров IP ядра со стороны процессора

1.2.2. Необходимо сделать сигналы rxd и txd сделать внешними для всей системы. Для этого:

System Assembly View -> <IP_core_name>_0 -> rxd -> Make External

System Assembly View -> <IP_core_name>_0 -> txd -> Make External

Система на базе процессора Microblaze в XPS готова. Для генерации файлов описания системы необходимо выполнить функцию “Generate Netlist” и убедиться в отсутствии ошибок. На рис. 1.1 приведена структурная схема разработанной на данном этапе системы.

Рис. 1.1 Структурная схема системы на базе процессора Microblaze с подключенным IP ядром UART

2015-05-10

2015-05-10 4004

4004