Эти два этапа можно комбинировать, либо проводить поочередно в зависимости от поставленной задачи. Но прежде всего, необходимо подготовить имеющийся проект в XPS для прошивки в ПЛИС.

3.1.Подготовка файлов конфигурации ПЛИС для разработанной системы.

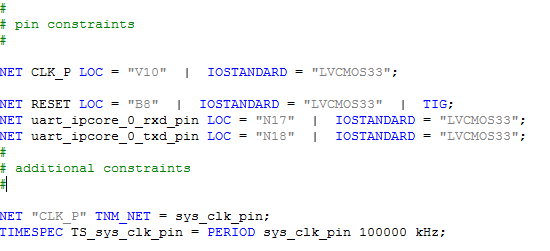

Во-первых, необходимо назначить правильные значения выводам микросхемы. Один из способов – править файл *.ucf вручную. В нашем случае файл lab_microblaze.ucf должен выглядеть следующим образом:

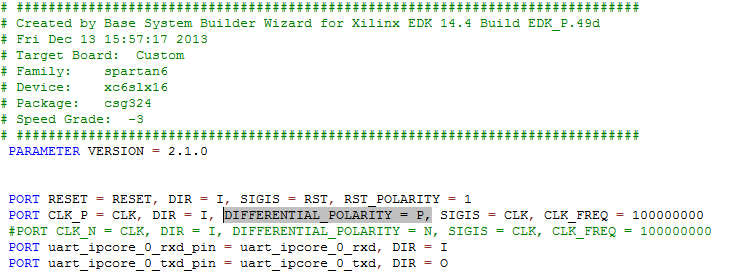

Во-вторых, следует обратить внимание на файл параметров системы lab_microblaze.mhs. Если внешний тактовый сигнал системы передается не дифференциальной парой, то для него необходимо исключить свойство DIFFERENTIAL_POLARITY и оставить положительную линию:

Далее необходимо заново сгенерировать Netlist, Bitstream, и экспортировать проект в SDK.

На этом завершена разработка аппаратной части проекта. Далее наступает этап разработки программного обеспечения для процессора.

3.2.Создание проекта в SDK и использование базовых функций чтения/записи в адресуемые регистры системы

В среде SDK необходимо создать проект: File -> New -> Application Project, выбрать шаблон и сгенерировать BSP.

Для управления IP-ядром UART со стороны процессора Microblaze необходимо организовать доступ к регистру управления и к регистру состояния модуля IP-ядра UART. Это можно реализовать с помощью функции Xil_Out32(<BASE_ADDR>,<DATA>) записи данных в регистр управления и функции Xil_In32(<BASE_ADDR>) чтения данных регистра состояний. Здесь BASE_ADDR – это базовый адрес IP-ядра в memory mapped структуре системы, указанный при ее проектировании в XPS. При этом необходимо помнить о том, что адресация осуществляется побайтово. Если, например, устройство с адресным пространством memory mapped имеет 2 адресуемых 32-битных регистра, то обращение к первому начинается с базового адреса (<BASE_ADDR> + 0х0), а ко второму – с базового адреса, сдвинутого на 4 байта (<BASE_ADDR> + 0х0).

Таким образом, для записи в регистр управления IP ядра UART (slv_reg1) необходимо использовать функцию Xil_Out32(<BASE_ADDR> + 0x4,<DATA>), а для чтения регистра состояний (slv_reg0) – функцию Xil_In32(<BASE_ADDR>).

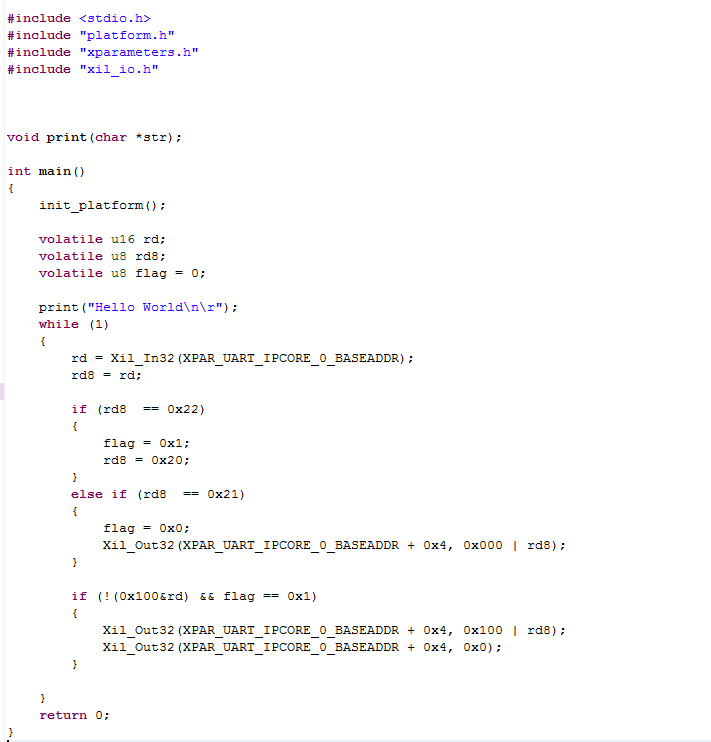

Для использования этих функций необходимо подключить заголовочный файл “xil_io.h”. В файле “xparameters.h” определены все адреса memory mapped устройств системы.

Для организации передачи данных по интерфейсу UART необходимо установить флаг начала передачи (8-й бит регистра управления) и данные для передачи (первые 8 бит регистра управления):

Xil_Out32(XPAR_UART_IPCORE_0_BASEADDR + 0x4, 0x100 | <DATA>);

Для чтения принятых данных по UART необходимо прочитать первые 8 бит регистра состояний:

A = Xil_Out32(XPAR_UART_IPCORE_0_BASEADDR);

3.3.Пример программы использования разработанного IP ядра UART

Ниже представлена небольшая программа на языке C для спроектированной системы. Программа реализует следующий алгоритм:

- по интерфейсу UART принимаются данные от внешнего устройства;

- как только на приемнике встретился символ «”», все принимающиеся данные транслируются внешнему устройству;

- как только на приемнике встретился символ «!», внешнему устройству ничего не транслируется.

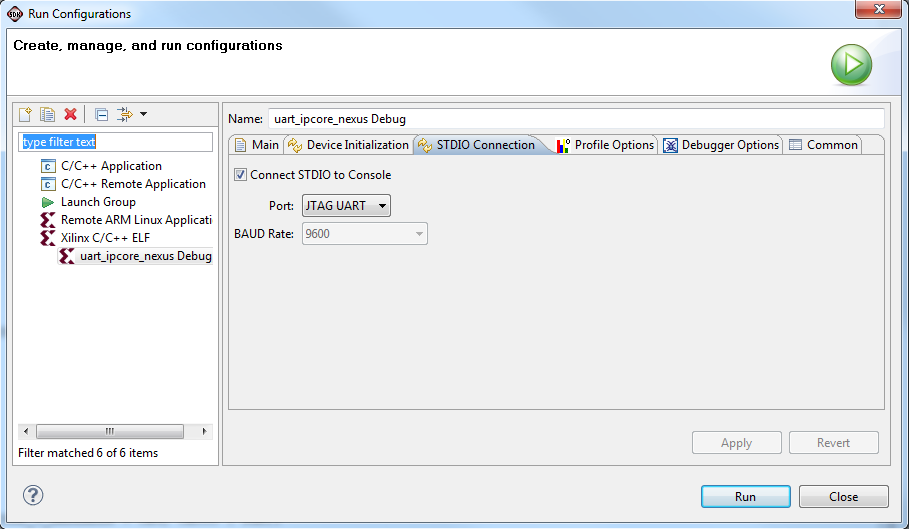

Для прошивки ПЛИС можно воспользоваться инструментами Xilinx Tools -> Program FPGA, где указать пути к файлам bitstream, созданным на завершающем этапе проектирования системы на базе процессора MicroBlaze в XPS. В поле Software Configuration можно добавить к прошивке ПЛИС elf-файл программы на C. В режиме bootloop программу нужно прошивать отдельно. Для этого необходимо перейти в следующее контекстное меню: Run -> Run Configurations, создать новую конфигурацию Xilinx C/C++ ELF, во вкладке STDIO Connection указать Connect STDIO to Console, Port:JTAG UART, RUN.

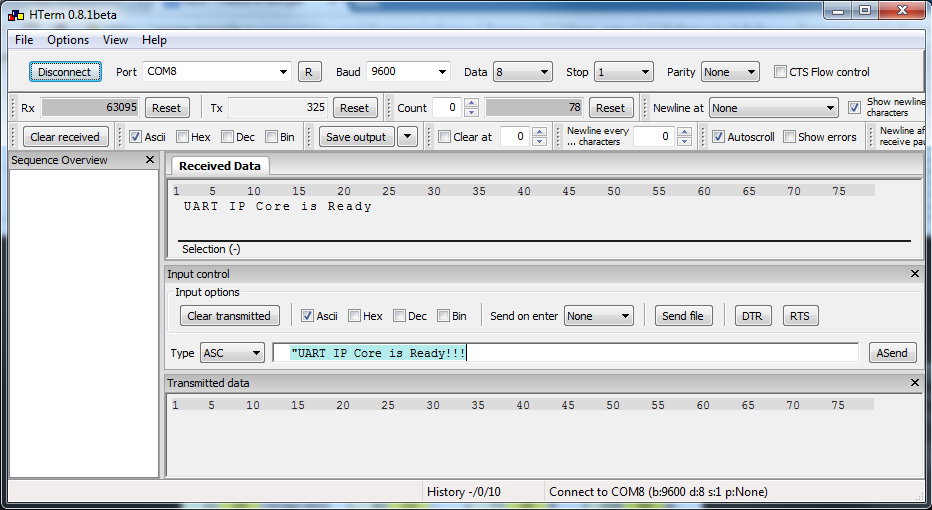

Результаты работы программы можно проверить с помощью программы на ПК hterm.exe:

2015-05-10

2015-05-10 2398

2398