Для підвищення продуктивності та швидкодії електронно-обчислювальних пристроїв застосовують багатопроцесорні (мультипроцесорні) системи, де на розв'язання задачі працюють не один, а декілька процесорів. У МП-86 здатність до роботи в таких системах передбачена можливістю функціонування в так званому максимальному режимі, котрий установлюється поданням напруги низького рівня на вивід MN/MX процесора. У мультипроцесорному режимі декілька мікропроцесорних модулів використовують один загальний ресурс: оперативну та дискову пам'ять, паралельний і послідовний інтерфейси та модеми, до яких вони приєднуються через багатопровідну системну шину.

Подібне розпаралелювання істотно підвищує продуктивність системи в цілому, однак породжує ряд проблем, пов'язаних з організацією безконфліктної взаємодії процесорів і спільного використання ресурсів системи. Дійсно, звернення до пам'яті або до зовнішніх пристроїв та захоплення системної шини дозволяється одночасно лише одному з процесорів, тоді як останні повинні в цей час переробляти раніш одержані дані або знаходитись у режимі очікування.

Такий часовий розподіл загальних ресурсів системи має назву арбітражу системної шини й виконується групою пристроїв (спеціальних ІМС) - так званих арбітрів шини. Арбітр шини дозволяє захоплення системної шини лише одному з процесорів, що виставили запит - тому, що з найвищим пріоритетом, - і забороняє вихід на системну шину всіх інших процесорів. По закінченні циклу обміну процесор звільняє системну шину й арбітр віддає її в розпорядження іншого процесора. Для встановлення пріоритетів використовують послідовний або паралельний спосіб арбітражу.

Послідовний спосіб арбітражу

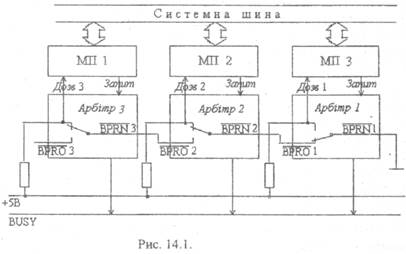

При послідовному способі арбітражу пріоритет процесорних модулів устанновлюється апаратно шляхом позамодульного послідовного з'єднання ІМС арбітрів (рис. 14.1).

Для послідовного арбітражу в арбітрів шини типу КР1810ВБ59 є вхід BPRN та вихід BPRO. Вихід попереднього арбітру, який має вищий пріоритет, приєднується до входу наступного арбітру з нижчим пріоритетом. На вхід арбітра з найвищим пріоритетом подається напруга низького рівня.

Усередині арбітра є перемикач, який з'єднує вхід арбітра BPRN із мікропроцесором, або з'єднує вхід арбітра з його виходом. Цей перемикач установлюється у верхнє положення запитом від мікропроцесора. За наявності запиту перемикач встановлюється у верхнє положення та якщо на вході відповідного арбітра є сигнал низького рівня, процесор одержує дозвіл на захоплення шини.

На зображеній схемі процесор МП1, що має найвищий пріоритет, запиту не робить, а його встановили МП2 та МПЗ. Сигнал низького рівня потрапляє на вихід МП2 з назвою Дозв2 і дозволяє МП2 захопити шину, тоді як МПЗ, хоч і зробив запит, але дозволу не одержить, бо напруга низького рівня до нього не доходить.

На проходження сигналу дозволу через ланцюжок арбітрів витрачається певний час, тому не рекомендується з'єднувати послідовно більше трьох арбітрів.

Паралельний спосіб арбітражу

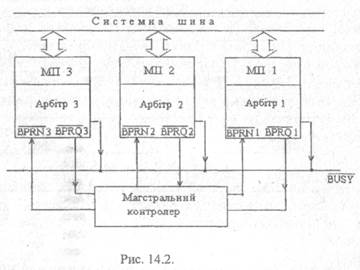

При паралельному способі арбітражу мікропроцесорний модуль, який має захопити системну шину, подає через свій арбітр сигнал BREQ (тобто сигнал запиту) до магістрального контролера (рис. 14.2). Цей контролер є логічною схемою, що складається з шифратора та дешифратора й саме він визначає пріоритети процесорних модулів. Вони можуть бути фіксованими або циклічно змінними. Звичайно магістральний контролер може керувати вісьмома арбітрами.

Одержавши запит від кількох модулів, контролер магістралі визначає найпріоритетніший і надсилає на його вхід BPRN - сигнал дозволу на захоплення системної шини. Одержавши дозвіл, відповідний арбітр виставляє на лінію BUSY низький рівень, яким він забороняє всім іншим арбітрам робити запити. Коли відповідний

процесор закінчує свою роботу й звільнює системну шину, сигнал BUSY знімається.

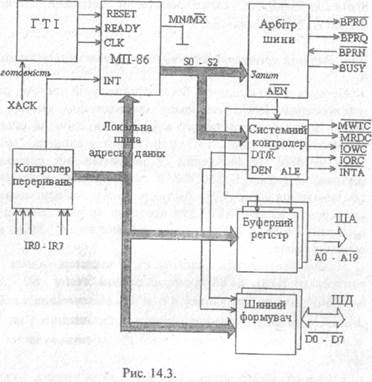

Робота процесорного модуля в мультипроцесорній системі

Процесор, що працює в багатопроцесорній системі, разом з усіма допоміжними ІМС, має назву процесорного модуля. Блок-схему такого модуля, спроможного керувати виходом на системну шину, зображено на рис. 14.3. До нього входить мікропроцесор КР1810ВМ86, установлений у максимальний режим, генератор тактових імпульсів К1810ГФ84А, три буферних регістри КР580ИР83 для виведення адрес А19 - АО та два двоспрямовані шинні формувачі з інверсією КР580ВА87 для введення та виведення даних. Усі ці елементи входили в блок-схему увімкнення МП-86 за мінімальною конфігурацією.

Новим елементом схеми є контролер шини (системний контролер) К1810ВГ88, який за словом стану SO - S2 виробляє керуючі сигнали для запису в пам'ять або читання з неї (МУУТСта MRDC), запису в зовнішні пристрої або читання з них (IOWC та IORC), а також сигнал згоди на обслуговування переривань ESTfA.

І нарешті, арбітр шини К1810ВБ59, який працює з уже знайомими нам сигналами ap6iTp^yBREQ,BPRN,Bl^RO,BUSY. Крім цих

сигналів є також лінії (і відповідні їм сигнали) INIT = RESET, ХАСК = READY, BCLK (синхронізація) і входи для запитів на немасковані переривання INT7 - INTO.

Своє бажання захопити системну шину мікропроцесор висловлює, видаючи слово стану SO - S2, в якому закладено код операції, що її хоче виконати мікропроцесор.

Своє бажання захопити системну шину мікропроцесор висловлює, видаючи слово стану SO - S2, в якому закладено код операції, що її хоче виконати мікропроцесор.

S2,S1,SO - 0 0 0 - згода на переривання;

О 0 1 - читання із зовнішнього пристрою; О 1 0 - запис у зовнішній пристрій;

0 1 1 - зупинка;

1 0 0 - видобування команди; 1 0 1 - читання з пам'яті;

1 1 0 - запису пам'ять;

1 1 1 - модуль не працює.

Слово стану подається на арбітр шини, який у відповідь на це формує запит на захоплення системної шини, і на контролер шини, який створює відповідний керуючий сигнал. Одночасно на вхід буферного регістра КР580ИР83 подається адреса, яка записується в ньому стробом ALE, що його формує системний

Слово стану подається на арбітр шини, який у відповідь на це формує запит на захоплення системної шини, і на контролер шини, який створює відповідний керуючий сигнал. Одночасно на вхід буферного регістра КР580ИР83 подається адреса, яка записується в ньому стробом ALE, що його формує системний

контролер. Але поки що ця адреса не потрапляє на системну шину й буферний регістр

знаходиться в третьому стані. Після цього на локальній (внутрішній) ШД ADO - AD 15 з'являються дані (якщо мова йде про запис), а також установлюється сигнал DT/R, що визначає напрямок руху цих даних.

Одержавши слово стану як сигнал про бажання мікропроцесора вийти на системну шину, арбітр починає діяти, намагаючись захопити її. Як це робиться, було вже розглянуто вище.

Одержавши дозвіл на захоплення системної шини, арбітр видає сигнал AEN, котрим він відкриває буферний регістр адреси й виводить адресу на системну шину, а також відкриває вихід системного контролера й "випускає" на системну шину утворений там керуючий сигнал. Разом із тим системний контролер сигналом DEN активізує шинний формувач КР580ВА87 і відкриває через нього шлях для даних.

Закінчивши машинний цикл, мікропроцесор знімає слово стану, повідомляючи арбітр про те, що роботу закінчено й системну шину можна звільнити.

2015-10-16

2015-10-16 1286

1286