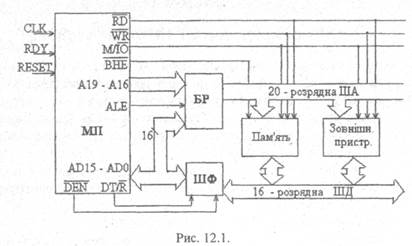

Блок-схему мікропроцесорного пристрою на процесорі КР181ОВМ86 зображено на рис. 12.1.

Мікропроцесор має 40 виводів. Більшу кількість їх не вдалося зробити з технологічних причин і через те тут не змогли виконати роздільно виводи ША та ПІД, як це було, наприклад, у МП-80. У МП-86 скорочення кількості виводів досягнуто шляхом суміщення (мультиплексування) функцій виводів ШД і ША: 16 виводів, позначених на рис. 12.1 як AD15 - ADO, у різні інтервали часу використовуються або як адресні виводи, або як виводи ПТД Але оскільки адреса має 20 розрядів, то передбачено ще 4 адресних виводи А19 - А16, на котрі видаються старші біти адреси. З виводівА19 - А16 та AD15 - ADO адреса через буферний регістр БР потрапляє на 20-розрядну ША й підтримується там протягом усього

машинного циклу. З цієї шини адреса потрапляє до пам'яті або до ЗП введення/виведення. Запис адреси в БР здійснюється за стробом адреси ALE, по негативному фронту якого буфер БР сприймає та фіксує адресу.

Призначено цю адресу для пам'яті чи для ЗП визначається сигналом М/ Ю (1 - пам'ят:ь(тетогу); 0 - зовнішній пристрій (input-output)). Напрямок обміну між МП та цими пристроями визначається сигналами RD та WR; RD = 0 здійснює сприймання даних до МП (читання), а при WR = 0 виконується запис інформації в пам'ять або в ЗП.

Обмін даними здійснюється через двоспрямований шинний формувач ШФ, який спрацьовує від строба DEN. Вибір напрямку передачі даних задається сигналом DT/ІЇ, котрий керує роботою ШФ (1 - від МП назовні (transmitting); 0 - до МП (reseaving)).

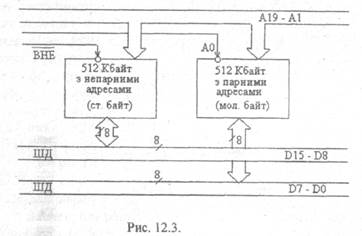

Сигнал ВНЕ визначає роботу блока пам'яті, його буде розглянуто згодом.

Синхросигнал CLK надходить від ГТІ й задає темп роботи всієї системи; RDY - сигнал готовності від пам'яті або від ЗП; RESET -апаратне скидання МП.

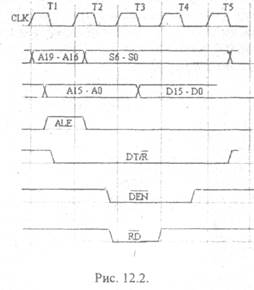

У першому такті ТІ на ША виводиться адреса А19 - АО. На виводах А15 - АО вона утримується до третього такту, а на виводах А19 - А16 замінюється в другому такті словом стану S6 - S3. Запис адреси в буфер БР здійснюється стробом ALE, який видається в першому такті. Сигнал напрямку передачі

даних DT/ R також установлюється в першому такті (при читанні цей сигнал має низький рівень).

У другому такті, після того, як адресу буде зафіксовано в буфері БР, шина AD15 - ADO перетворюється на шину даних. Сигнал DEN = 0 наприкінці 12 відкриває ШФ, а сигнал RD = 0 указує, що відбувається акт читання, який триває весь третій такт. Наприкінці четвертого або п'ятого такту всі сигнали знімаються. Аналогічно відбувається акт запису даних.

Слово стану S6 - S3 складається з чотирьох розрядів, які по лініях А19-А 16 передаються після того, як адресу буде зафіксовано в буфері БР. Значення цих бітів розглядатиметься далі.

Організація нам 'яті

Особливість МП-86 полягає в тому, що він є перехідним етапом від простих 8-розрядних процесорів до багаторозрядних. Тому для того, щоб мати можливість використовувати програми та комплектуючі ІМС, які були розроблені для 8-розрядних мікропроцесорів, у МП-86 передбачена можливість працювати як з

Часові діаграми роботи процесора

Часова діаграма машинного циклу читання зображена на рис. 12.2.

Цей цикл триває такти.

8-розрядними, так і з 16-розрядними даними. Це дещо ускладнює його апаратну частину.

Блок пам'яті МП-86 складаєьтся з 8-розрядних комірок пам'яті, кожній з яких привласнюється 20-розрядна двійкова адреса. Дані можна записувати в пам'ять (або зчитувати з неї) у вигляді 8-розрядних байтів або 16-розрядних слів. В останньому випадку мають бути задіяні дві суміжні комірки пам'яті. Така двоїстість відображається на організації пам'яті та роботі з нею.

Таблиця 12.1

Уся пам'ять складається з двох блоків: блоку комірок із парними адресами та блоку комірок із непарним адресами. Кожний із них може містити до 512 Кбайтів і керуватися окремо (рис. 12.3.).

До обох блоків надходять лінії ША А19 - А1. До блоку парних адрес надходить також лінія АО, а до блоку непарних - лінія ВНЕ. Блоки спрацьовують, якщо на цих лініях буде низький рівень (0). При роботі з 16-розрядним словом дані з блоку парних КП видаються на молодші розряди ШД, а з блоку непарних КП - на старші розряди ШД. Результати, які одержуються при різних комбінаціях сигналів АОта ВНЕ подано в табл. 12.1.

Як видно, при комбінації ВНЕ = 0 та АО = 0 на шину даних видається ціле 16-розрядне слово, що складається зі старшого та молодшого байтів. При ВНЕ = 0 та АО = 1 видається лише старший

| Вміст КП з | Вміст КПз | |||

| ВНЕ | АО | непарнною адресою | парною адресою | Результат |

| Так | Так | Слово | ||

| Так | Ні | Ст. байт | ||

| Ні | Так | Мол, байт | ||

| НІ | Ні | Немає обміну |

байт. А при ВНЕ = 1 та АО = 0 лише молодший. При комбінації 11 пам'ять відключена.

Така організація пам'яті дозволяє гнучко видавати або слова, або байти. Звідси ж випливає, що при запису слова останньому слід надавати парну адресу. Тоді при його зчитуванні достатньо буде вказати парну адресу та видати сигнал ВНЕ ~ 0. У цьому разі слово записується та зчитується за один машинний цикл. Можна, звичайно, записувати слово і по частинах: старший байт за парною адресою, а молодший - за непарною, Тоді й записувати, і видобувати слово доведеться за два заходи, втрачаючи на це два машинні цикли. А це, звичайно, знизить швидкодію системи.

Організація переривань

У мікропроцесорі МП-86 можуть бути переривання трьох типів:

- зовнішні, що не можуть бути замасковані;

- зовнішні, що можуть бути замасковані;

- внутрішні.

Запит на зовнішні переривання, які не можуть бути замасковані, здійснюється через вхід NMI. Вони використовуються в найбільш відповідальних випадках, наприклад, за аварійної зупинки мікропроцесора.

Звичайні переривання від зовнішніх пристроїв можуть бути замасковані (заборонені) програмними засобами. Запити на" них подаються на вхід INTR.

Внутрішні закладаються в програму й викликають до дії підпрограми, закладені фіксовано до ПЗП машини.

Особливості адресації в МП 86

Основна особливість адресації в МП-86 полягає в тому, що адреса, за якою звертаються до пам'яті, має 20 розрядів, тоді як розмір слова складає лише 16 таких. Найпростіше, здавалося б, цю проблему можна було розв'язати шляхом "прибудовування" до блоку 16-розрядної адреси ще чотирьох старших бітів, які б "озаголовлювали" цей блок ("сторінку") в пам'яті1. Однак ці блоки були б надто громіздкими, бо їх об'єм становив би 64 Кбайти і маніпулювати з ними було б незручно.

Тому в МП-86 застосовується більш гнучка система формування виконавчої (фізичної) адреси. Фізична адреса, тобто адреса комірки пам'яті, до якої звертаються, одержується шляхом підсумовування двох зсунутих одне щодо одного 16-розряднних слів. Одне з них має назву базової адреси й зберігається в спеціальних так званих сегментних регістрах (інші назви: сегментна адреса, сегмент, база). Друге слово, що має назву ефективної адреси (або зміщення, внутрішньосегментне зміщення, відносна адреса), зберігається в регістрах загального призначення (робочих регістрах). Сукупність цих двох адрес має назву логічної адреси.

Для формування фізичної адреси 16-розрядну базову адресу зсувають ліворуч на 4 двійкові розряди, а молодші розряди, що лишилися, заповнюють нулями. До 20-розряАного числа, яке при цьому утворилось, додають 16-розрядне зміщення, їх сума і є фізичною адресою. Так, наприклад, при базовій адресі 123АН і зміщенні 3418Н процедура формування фізичної адреси матиме такий вигляд:

123АО + 341В 157ВВ - фізична адреса

Базова адреса звичайно встановлюється та зберігається незмінною протягом виконання всієї програми. Уся свобода дії сконцентрована лише в зміщенні, яке програміст може варіювати як завгодно на свій

розсуд.

1 Така "сторінкова" адресація застосовується в нових ЕОМ, починаючи з 80386.

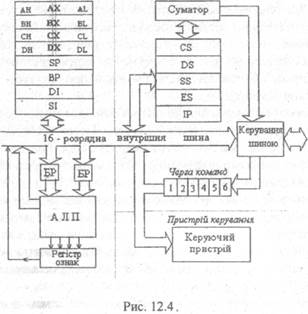

Операційний пристрій

Пристрій спрлжіння з зовнішньою шиною

Основою операційного пристрою є АЛЛ, котрий, власне, і виконує обробку інформації. З внутрішньою ПІД АЛЛ поь'язаний через буферні регістри. Якісний характер результатів фіксується в регістрі ознак. Уся ця частина не відрізняється принципово від аналогічної частини МП-80.

Іншу структуру мають регістри загального призначення (робочі регістри), їх чотири: АХ, ВХ, СХ і DX. Вони 16-розрядні й у них можна розміщати двобайтові слова. Але ці самі регістри можна використовувати й "по половинках", записуючи один байт у старшу половину регістра (наприклад, у ВН), а другий - у молодшу (наприклад, у BL) і працювати з цими байтами окремо один від одного.

Робочі регістри МП-86 мають кожний своє специфічне призначення. Цим вони відрізняються від робочих регістрів МП-80, де всі регістри (крім А) рівноцінні. Регістр АХ використовується звичайно при арифметичних операціях із двобайтовими операндами. Регістри АН та AL можуть також бути використані для подібних цілей при роботі з однобайтовими операндами.

Регістр ВХ вживається для непрямої адресації даних. Тим він подібний до HL-пари в МП-80. Регістр СХ виконує звичайно функції лічильника в програмних циклах. Регістр DX бере участь у операціях з множення та ділення слів, він може також бути використаний і для зберігання даних. Але цей розподіл функцій є значною мірою умовним і стосується програмного використання регістрів. З апаратного ж погляду всі ці регістри рівноцінні та кожний із них може виконувати функції іншого.

Двобайтові регістри ВР, SP, SI, DI утворюють групу показникових та індексних регістрів. У них містяться зміщення, що використовуються для формування фізичної адреси. З них лише регістр SP - показник стеку - має аналог у МП-80. Для інших регістрів таких аналогій знайти не вдається.

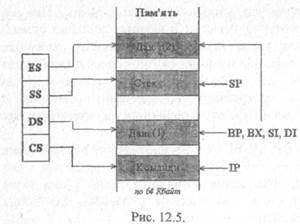

Пристрій спряжіння з шиною також містить групу двобайтових регістрів. Регістри CS, DS, SS та ES мають назву сегментних регістрів і в них розташовуються базові адреси відповідних програмних сегментів. Регістр CS містить базову адресу сегмента команд; DS є базою сегмента даних; SS - база сегмента стеку; ES -резервний сегмент. Регістр IP є лічильником команд. У табл. 12.2. та на рис. 12.5 указується, як звичайно комбінується вміст робочих і базових регістрів для утворення фізичної адреси.

Таблиця 12.2.

| Тип звернення до пам'яті | База | Зміщення | Примітки |

| Вибірка команди | CS | IP | |

| Стекова операція | SS | SP | |

| Звернення до змінної | DS | ЕА | Базою можуть бути також CS, SS, ES |

| Ланцюжок - джерело | DS | SI | |

| Ланцюжок - приймач | ES | DI |

Ефективна адреса ЕА формується вмістом регістрів ВХ, ВР, SI, DI та їх комбінаціями. Фізична адреса формується шляхом відповідного підсумовування бази й зміщення, котре виконується суматором адреси.

Цікавою особливістю пристрою спряжіння з шиною в МП-86 є регістр черги адрес. За його допомогою можна в проміжки часу, коли

процесор зайнятий виконанням раніш сприйнятої команди, робити вибірку ряду наступних команд. Вибрані команди фіксуються у зсувному регістрі команд, що складається з 6 комірок пам'яті, і утворюють чергу команд, підготовлених до виконання. Таким

чином можливо використовувати системну шину протягом майже 100% часу й збільшувати загальну швидкодію ЕОМ. Щоправда, коли в програмі зустрічається команда переходу (умовного чи безумовного), або ж команда переходу до підпрограми, черга ламається й установлюється нова, що відповідає новим фрагментам задачі.

Структура регістра ознак, принаймні в молодших бітах, подібна до структури ознак МП-80, лише до назви біта додається літера F. Ці біти мають назву прапорів.

Старший байт Молодший байт

| X | X | X | X | OF | DF | IF | TF | SF | ZF | X | AF | x |pf | X | CF |

У старшому байті біт OF сигналізує про переповнення; біти DF, IF, та TF установлюються програмне. Наприклад, установленням IF = 0 можна маскувати (забороняти) переривання. Прапор DF визначає напрямок обробки програм - ланцюжків; Прапор TF = 1 переводить МП у режим трасування, тобто покрокового виконання команд. Це буває корисно при налагоджуванні програми.

Тепер можна повернутися до слова стану, що задається сигналами S6 - S3. Ці сигнали формує сегментний регістр, що бере участь в утворені фізичної адреси. Іншими словами, ці сигнали вказують, до

якого сегмента пам'яті виконується звернення в даному машинному циклі. Прийнято таке кодування сегментів:

. S4,S3 = 00 резервний сегмент ES; 01 сегмент кодів CS;

10 сегмент стека SS;

11 сегмент даних DS.

Сигнал S5 відповідає стану прапора IF: S5 =0 - переривання заборонені; S5 =1 - переривання дозволені. Прапор S6 не використовується.

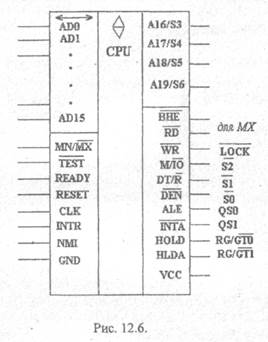

Наприкінці повернемося до позначення виводів МП-86, Як зазначалося, їх сорок. Призначення більшості з них нам вже знайомі. Це мультиплексовані виводи адреси та даних AD15-ADO. Старші біти адреси А19-А16 мультиплексовані з бітами слова стану S5 -S3.

Сигнал ВНЕ визначає дозвіл на старший байт

даних.

RD та WR -

сигнали читання та запису в пам'ять або зовнішній пристрій.

М/ІО визначає чи то є звернення до пам'яті (1), чи до зовнішнього пристрою (0).

ALE - строб для запису адреси в буферний регістр.

DT/R - визначає напрямок руху інформації через шинний формувач даних; сигнал DEN активізує (відкриває) його.

INTR та INTA - запит та згода на переривання. NMI - запит на незамасковане переривання. HOLD та HLDA - запит та згода на ПДП.

CLK, READY, RESET - знайомі нам сигнали синхронізації, готовності та скидання.

MN/MX визначає режим роботи МГІ-86 - мінімальний або максимальний (багатопроцесорний, тобто паралельно з іншими процесорами, наприклад, зі співпроцесором). У максимальному режимі призначення деяких виводів змінюється, що й показано на рис. 12.6 окремо. Сигнали LOCK, TEST, QSO, QS1, RG/GTO, RG/GTi використовуються в роботі зі співпроцесором, про, що мова йтиме далі.

Виводи VCC та GND - живлення ІМС.

2015-10-16

2015-10-16 584

584