3(1)

Глава 10

117

10.11. Дополнительные примеры с решениями

В данном параграфе представлены примеры, решение которых требует применения интегральных микросхем счётчиков и делителей частоты совместно с ИМС иного функционального назначения (компараторы, дешифраторы, триггеры, мильтиплексоры и др.), а также примеры на применение методов проектирования счётчиков, рассмотренных в параграфе 10.8 и в приложении к главе10.

Пример 1. С использованием двоичных счётчиков и других ИМС постройте схему, реализующею управление циклическим опросом восьми измерительных преобразователей температуры в напряжение. Преобразователи П0, П1,...,П7 выполнены в виде четырёхплечих мостов, не имеющих друг с другом общих точек. Выходное напряжение U0, U1,...,U7 преобразователей П0,...,П7 изменяются в диапазоне от -0,1В до +9В. Проектируемая схема должна осуществлять передачу информационных сигналов в двухпроводную линию связи. Продолжительность опроса одного преобразователя составляет 50 мкс.

Решение

1. Полагаем, что преобразователи П0, П1,...,П7 имеют двоичные адреса {000}, {001},…,{111}. Тогда при подаче на вход счётчика счётных импульсов с частотой f, равной

|

|

может быть выполнено последовательное формирование двоичных адресов преобразователей П0,...,П7 в циклическом режиме, так как указанные адреса повторяются на выходах счётчика после подсчёта каждых восьми импульсов. Где Т - время фиксации каждого двоичного адреса (продолжительность опроса одного преобразователя Пj). При этом цикл опроса всех датчиков равен Тц= 8Т = 8 · 50 = 400 мкс.

2. Мостовые преобразователи П0, П1,...,П7 имеют по две выходные линии Xj и Yj соответственно. Где j  {0,1,2...,7}. Для коммутации указанных линий могут быть применены аналоговые восьмиканальные

{0,1,2...,7}. Для коммутации указанных линий могут быть применены аналоговые восьмиканальные

119

|

|

120

мультиплексоры КМОП серии ИМС К561, либо К564 так как они срабатывают с задержкой не превышающей 400 мкс, а их входное напряжение находятся в пределах от -0.2В до (Еп +0,2)В при допустимом диапазоне напряжения питания Еп=(3,…,15)В, что перекрывает диапазон напряжений U0,...,U7, формируемых преобразователями П0,...,П7. При этом коммутация линий Xj и Yj, принадлежащих одному и тому же преобразователю, может быть реализована с помощью двух разных микросхем мультиплексоров с идентичной их адресацией

3. С учётом изложенного выше проектируемая схема приобретает вид, показанный на рис.10.46. В данной схеме генератор G генерирует непрерывную последовательность импульсов с частотой 20 кГц, которая поступает на счётный вход суммирующего счётчика К561ИЕ10 (DD1). На выходах счётчика {Q4,Q2, Q1} адрес опрашиваемого преобразователя изменяется на +1 после каждого счётного импульса в пределах одного цикла опроса. Затем адресные двоичные комбинации {Q4,Q2,Q1} повторяются. Выходы {Q4,Q2, Q1} счётчика (DDl) соединены с адресными входами мультиплексоров К561КП2 (DD2) и (DD3), на информационные входы которых поступают сигналы Xj, Yj от преобразователей П0,...,П7. Таким образом, к двухпроводной линии связи в любой момент времени оказывается подключённым один из измерительных преобразователей П0, П1,...,П7, а в течение цикла опроса Тц = 400 мкc оказываются опрошенными все восемь преобразователей.

Пример 2. Спроектируйте схему, формирующую на своём выходе импульсную последовательность сигналов с частотой fвых = 10Гц при подаче на её вход импульсов с частотой fвх = 581250Гц. Амплитуда входных и выходных сигналов должна быть не менее 9В.

Решение

1. В соответствии с условиями задачи проектируемая схема должна выполнять деление частоты входных импульсов с коэффициентом деления Кд, равным

|

|

2. Из известных ИМС делителей частоты (см. таблицу 10.13) наиболее высокий коэффициент деления Кдшах = 21327 имеют программируемые интегральные микросхемы КА561ИЕ15А,Б (КР564ИЕ15В), что недостаточно для обеспечения заданного коэффициента деления частоты, равного 58125. Поэтому для построения проектируемой схемы применим ИМС типа КА561ИЕ15Б совместно со счётчиком на двух JK - триггерах, модуль счёта которого К = 3. Тогда ИМС КА561ИЕ15Б должна быть запрограммирована на реализацию коэффициента деления К′д, равного

|

|

3. Выполним действия, необходимые для программирования ИМС КА561ИЕ15Б на её работу в режиме деления частоты с коэффициентом деления К′д = 19375:

• Разложение К′д по модулю М = 8 даёт

К′д =19375 = 8·2421 + 7

Откуда имеем: Р5 =7 и {J3J2J1} = {111}

• в соответствии с представленным выше разложением число тысяч равно 2. Однако из таблицы 10.14 видно, что для отображения множителя тысяч Р1 предусмотрен при М = 8 только один двоичный разряд J4. Поэтому принимаем P1 = 1 => {J4} = 1, а "избыточную" тысячу переносим в разряд сотен, увеличивая их множитель Р2 на 10, То есть, имеем

Р2 =10 +4 = 14 => {J16J15J14J13} = {1110}

•••Множитель десятков Р3 = 2 => {J12J11J10J9} = {0010} и множитель единиц Р4 =1=>{J8J7J6J5} = {0001} определяется непосредственно из разложения К′д.

•••• Для реализации режима деления частоты с модулем М = 8 на входы L и {K3K2K1} ИМС КА561ИЕ15Б должны быть поданы следующие сигналы (см. таблицу 10.14):

122

L = 0; {К3К2К,} = {100}

• • • • • В соответствии с соотношением (10.54) имеем

К′д=М(103Р1 + 102·Р2 + 101·Р3+Р4) + Р5=8(103·1 + 102·14+101·2 + 1) +7 = 19375

4. Проектируемая схема представлена на рис. 10.47. Она состоит из двух блоков, соединённых каскадно:

• делителя частоты КА561ИЕ15Б (DD1), запрограммированного на работу с коэффициентом деления К′д равным 19375

• суммирующего синхронного двоичного счётчика, выполненного на двух JK - триггерах К561ТВ1 (DB2.1; DD2.2) с модулем счёта К = 3. При этом модуль счета К = 3 получен за счёт введения обратной связи с выхода  триггера DD2.2 на J –вход триггера DD2.1.

триггера DD2.2 на J –вход триггера DD2.1.

5. Коэффициент деления Кд схемы рис. 10.47 равен

Кд = К΄д · К = 19375 • 3 = 58125

6. Для обеспечения амплитуды выходных импульсов Uвых.m  9 В напряжение питания Еп ИМС DD1, DD2 принято равным 10В.

9 В напряжение питания Еп ИМС DD1, DD2 принято равным 10В.

7. (Для самостоятельного решения). Не изменяя структуру построения схемы рис. 10.47, выполните действия, в результате которых на её выходе Fвых будет формироваться последовательность импульсов с часто

той fвых равной

• 8,33 Гд;

• • 7,14 Гц;

• • • 10 Гц.

В каждом из указанных случаев частота входных импульсов fвх остаётся неизменной и равной 375 кГц.

123

Пример 3. Разработайте схему устройства, формирующего на своих выходах FA, Fb, Fc трёхфазную систему напряжений UA, Ub, Uc. Назначение схемы: работа в цепях управления трёхфазными автономными инверторами напряжения и тока; работа на трёхфазную шину управления матрицами ПЗС и др. Формирование напряжений UA, UB, Uc должно удовлетворять следующим условиям:

• В течение полупериода трёхфазной системы напряжений напряжение Uj должно соответствовать "единичному" логическому уровню, а в течение следующего полупериода "нулевому" логическому уровню. Где j  {A,B,C}.

{A,B,C}.

• Напряжения UA, Ub, Uc, должны иметь точную фазировку, определяемую сигналами тактового генератора G.

• Между напряжениями UA, Ub, Uc, должен реализоваться взаимный сдвиг по фазе на ⅓ периода Т трёхфазной системы напряжений.

Решение

1. Анализ условий поставленной задачи показывает, что для точной фазировки напряжений Ua, Ub, Uc между частотой f трёхфазной системы напряжений и частотой тактового генератора fG должно выдерживаться следующее соотношение:

fG = 6·f.

С учётом этого для построения проектируемого устройства целесообразно использовать счётчик с модулем счёта К=6. В качестве такого счётчика может быть использован стандартный ТТЛ счётчик-делитель ИЕ4, который может реализовать модуль счёта К=2, К=6, К=12.

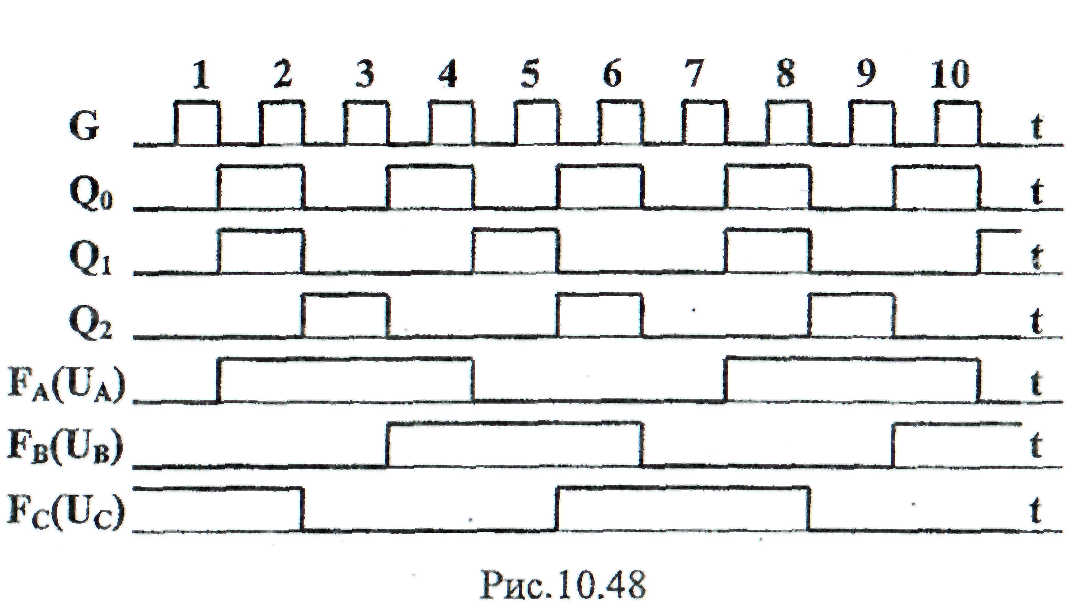

2. Для обоснования дальнейших этапов проектирования устройства построим временные диаграммы работы счётчика во взаимной их привязке к временным диаграммам тактового генератора G и трёхфазной системы напряжений UA, UB, Uc. Указанные временные диаграммы приведены на рис.10.48.

3. На основе анализа временных диаграмм рис.10.48 построим диаграммы Вейча-Карно (см. рис. 10.49а, б, в) для логических функций FA, Fb, Fc реализуемых на выходах проектируемой схемы в зависимости от комбинации сигналов {Q1Q2Q3} выходах счётчика.

124

|

|

4. Анализ диаграмм Вейча-Карно рис. 10.49 даёт следующие результаты:

FA = Q0·  2 +

2 +  o Q2 = Qo ⊕ Q2

o Q2 = Qo ⊕ Q2

FB = Qo·  1 +

1 +  0Q1 = Qo

0Q1 = Qo  Q1

Q1

Fc =  0

0  1

1  2 +

2 +  oQ1Q2 + Q0Q1

oQ1Q2 + Q0Q1  2 + Qo

2 + Qo  1Q2 =

1Q2 =  0(

0(  1

1  2 + Q1Q2) +

2 + Q1Q2) +

+Q0(Q1  2+

2+  1Q2) =

1Q2) =  0(

0(  ) + Q0(Q1⊕Q2) = Q0⊕(

) + Q0(Q1⊕Q2) = Q0⊕(  )

)

5. С учётом полученных результатов проектируемая схема принимает вид, показанный на рис.10.50. В схеме рис.10.50 применены следующие ИМС: DD1 - К155ИЕ4; DD2 - КР1533ЛП5; DD3.1 - КР1533ЛН1.

6. Примечания: 1. В счётчике DD1 выход Q0 первой секции (делитель на 2) не соединялся со входом второй его секции (делитель на 6), выходы которой Q1 и Q2 являются выходами фрагмента счётчика с модулем К=3.

2. При формировании логического уравнения для выходного сигнала Fc мы исходим из необходимости построения логической части схемы проектируемого устройства на однотипных элементах с минимальным количеством корпусов ИМС.

7. (Для самостоятельного решения). Разработайте схему устройства, аналогичного по реализуемым функциям устройству рис.10.50, используя при этом реверсивный двоичный счётчик типа КР1554ИЕ7

1СР1533ИЕ7). Постройте временные диаграммы работы устройства при прямом и обратном счёте счётчика. Проанализируйте, что происходит с трёхфазной системой напряжений UA, Ub, Uc при реверсировании управления счёта.

125

|

|

Пример 4. Разработайте устройство формирующее на его выходах Y1, Y2 последовательности импульсных сигналов с частотами f1,f2 в соответствии с таблицей 10.19. Где f1 - частота сигналов Y1, f 2 - частота сигналов Y2. Управление режимом работы устройства осуществляется схемой управления (СУ) путем подачи на его входы двоичных управляющих кодовых комбинаций {A1,Ao}. Устройство предназначено для работы в составе аппаратуры на основе ТТЛ (ТТЛШ) ИМС.

Таблица 10.19

| Сигналы управления {A1,A0} | Частота сигналов Y1 и Y2 | |

| f1, МГц | h, МГц | |

| 00 | 30,0 | 0,03 |

| 01 | 3,0 | 0,3 |

| 10 | 0,3 | 3,0 |

| 11 | 0,03 | 30,0 |

Решение

1. Анализ таблицы 10.19 показывает, что диапазон частот импульсных сигналов, формируемых проектируемым устройством, простирается от fj min = 0.03 МГц до fj max = 30 МГц. Где j  {1,2}. При этом дискретный ряд частот 0,03 МГц, 0,3 МГц, 3,0 МГц и 30,0 МГц включает частоты, отличающиеся от fj max=30 МГц в 10;100 и 1000 раз. Поэтому принимаем вариант построения схемы устройства, при котором формирование сигналов наиболее высокой частоты fj max=30МГц осуществляет генератор G, работающий в автогенераторном режиме, а сигналы более низких частот формируются путем деления частоты fj max в 10,100 и 1000 раз. Структурная

{1,2}. При этом дискретный ряд частот 0,03 МГц, 0,3 МГц, 3,0 МГц и 30,0 МГц включает частоты, отличающиеся от fj max=30 МГц в 10;100 и 1000 раз. Поэтому принимаем вариант построения схемы устройства, при котором формирование сигналов наиболее высокой частоты fj max=30МГц осуществляет генератор G, работающий в автогенераторном режиме, а сигналы более низких частот формируются путем деления частоты fj max в 10,100 и 1000 раз. Структурная

127

схема, реализующая описанный выше принцип формирошшин импульсных последовательностей с частотой 30МГц, ЗМГц, 0,3 МГц и 0,03МГц показана на рис.10.51.

|

|

2. Для построения электрической схемы проектируемого устройства выбираем ИМС ТТЛШ серии КР1533, счетчики которой могут работать в режиме деления частоты при частоте тактовых сигналов  32 МГц.

32 МГц.

3. В качестве делителя частоты с коэффициентом деления Кд=10 используем ИМС четырехразрядных двоичных счетчиков КР1533ИЕ5. ИМС этого типа содержат 4 триггера, срабатывающие по отрицательному фронту импульса. Для получения счетчика-делителя с Кд=10 на основе КР1533ИЕ5 используем следующие внешние связи (см. рис. 10.52):

• Выход (12) счетчика-делителя на 2 соеденим со входом (1) трехразрядного счетчика-делителя на 8.

• Выходы (9) и (11) трехразрядного счетчика соеденим со входами (2) и (3) предустановки счетчика.

4. Коммутация заданных последовательностей импульсных сигналов со значениями частот f1, f2 в соответствии с таблицей 10.19 на выходы Y1 и

128

|

|

129

Y2 проектируемого устройства может быть выполнена с помощью сдвоенного мультиплексора КР1533КП12. При этом управляющие сигналы {A1,A0} схемы управления должны быть поданы на адресные входы мультиплексора, а на его информационные входы должны быть поданы импульсные сигналы с частотой 30 МГц; 3 МГц; 0,3 МГц и 0,03 МГц в порядке, определяемом таблицей 10.19.

5. Схема проектируемого устройства, построенная с учетом представленных выше материалов, приведена на рис. 10. 52. В данной схеме применены следующие ИMC:DD1, DD2, DD3 - KP1533ИE5, DD4 - КР1533КП12.

Пример 5. Спроектируйте распределитель импульсов для схемы управления регулируемым трехфазным мостовым выпрямителем. Метод управления - дискретный. Частота сетевого напряжения - 400Гц. Структурная схема, реализующая дискретный метод управления, приведена на рис.10. 53. Обозначения принятые на схеме рис.10. 53:

(Ud, Ud3) - среднее значение выпрямленного напряжения и его заданное значение; fc - частота сетевого напряжения (fc=400Гц); fm - частота импульсных сигналов генератора ГИ; m - эквивалентное число фаз выпрямителя; Uрас - напряжение рассогласования между Ud и Ud3 (Upac=U(Ud - Udз); Uy - напряжение на выходе усилителя рассогласования (Uy=ky• Upac); Ф1,..., Фм - выходы формирователей сигналов управления тиристорами VS1,..., VS6 выпрямителя.

Решение

1.В трехфазном мостовом выпрямителе ток нагрузки протекает всякий раз через два тиристора, один из которых расположен в катодной группе, а другой - в анодной. Проводимость каждого тиристора

130

= 2π /3,

= 2π /3,

а интервал совместной работы тиристоров при угле регулирования α=0 равен π/З. За период Тс напряжения сетевого питания происходит шесть переключений тиристоров VS1,VS2,...,VS6 во время которых реализуется их включение с помощью сигналов управления, поступающих от распределителя импульсов через формирователи, и последующее выключение под действием линейного напряжения сети.

Выпрямитель работает в 6 тактов и его эквивалентное число фаз m равно

m=6.

2.С учетом изложенного в п.1 проектируемый распределитель импульсов должен формировать на своих выходах F1, F2,...,F6 циклически повторяющиеся с частотой fc импульсные сигналы, смещенные друг относительно друга на 1/6 часть периода Тс сетевого напряжения. При этом их длительность tи и пауза tп должны быть равны соответственно:

tи=Tc / 6 tп=Тc - tи

где Тс=1 / fc=l/400=2,5•10-3 c=2,5 мс

Откуда имеем:

tи=2,5•10-3 /6=4,17•10-4=0,417мс

tп=2,5•10-3-4,17•10-4=2,083•10-3c=2,083мс

3.Частота fm импульсного генератора ГИ, тактирующего проектируемый распределитель импульсов, определяется из соотношения:

131

fm= m•fс= 6•400=2400Гц=2,4кГц

4.Анализ расчетных данных п.2 и п. 3 показывает, что проектируемый распределитель импульсов имеет сравнительно невысокое быстродействие, что позволяет применить для его построения ИМС любых промышленных серий ТТЛ и КМОП технологии. Для конкретизации схемного построения данного распределителя импульсов и в продолжение изучения ИМС серии КР1533 реализацию проектируемого устройства выполним на следующих ИМС:

• КР1533ИЕ2 - четырехразрядный двоично-десятичный счетчик,включающий две секции: счетчик - делитель на 2 и счетчик - делитель на 5;

• КР1533ИД7 -дешифратор-демультиплексор 3 на 8.

5.Схема проектируемого распределителя приведена на рис. 10.54, а временные диаграммы, поясняющие его работу представленны на рис. 10.55.

6. (Для самостоятельного решения). Спроектируйте распределитель импульсов для схемы управления шаговым двигателем с учетом того, что он должен работать в четыре такта. Проиллюстрируйте работу распределителя временными диаграммами.

Примечание: Каждому импульсу распределителя соответствует поворот ротора двигателя на фиксированный угол, а его скорость вращения пропорциональна частоте импульсов распределителя. Более подробно см., например, в книге: Элементы автоматического управления и контроля/Н.И.Подлесный, В.Г.Рубанов. - К.: Вища школа. Головное изд-во. -1992. -477 с.

132

| +Еп |

| К формирователям импульсов управления тиристорами |

| 11вых |

|

|

| 7_ 6 Feux |

Пример 6. На основе ИМС серии KP1533 разработайте цифровое устройство регулируемой задержки импульсов. Устройство должно формировать на своем выходе Fвых, импульсы Uвых, задержанные на время Тзд относительно момента Т0 появления на его входе Fвх запускающего импульса U3. Значение Тзд может изменяться в пределах от 0 до Тзд.max=25,5мкс с шагом ∆Тзд=0,1мкс. Величина Тзд определяется численным значением кода управления Ny. Зависимость Тзд от Ny должна быть линейной.

Решение

1.Построение проектируемого устройства может быть выполнено в соответствии со структурной схемой рис.10.56, включающей

генератор тактовых импульсов G, программируемый делитель частоты (ПДЧ) на основе счетчика и цифрового компаратора (см. рис. 10.26.а) и JK -триггер.

В исходном состоянии JK -триггер находится в «нулевом» состоянии (Q=0;  =l), число N, зарегистрированное в счетчике программируемого делителя, равно нулю (N=0) и текущий счет тактовых импульсов запрещен «нулевым» сигналом на его входе разрешения счета ЕСТ (ECT=Q=0). После подачи запускающего импульса U3 триггер устанавливается в «1» состояние (Q=1), в результате чего ЕСТ=1 и каждый очередной тактирующий импульс генератора G будет увеличивать число N в счетчике ПДС на единицу. Импульсный сигнал Uвых появится на выходе Fвых проектируемого устройства после того, как число N станет равным числу Ny. При этом сигналом обратной связи с выхода Fвых ПДЧ на К -вход JK - триггера последний будет переведен в «0» -состояние и своим сигналом

=l), число N, зарегистрированное в счетчике программируемого делителя, равно нулю (N=0) и текущий счет тактовых импульсов запрещен «нулевым» сигналом на его входе разрешения счета ЕСТ (ECT=Q=0). После подачи запускающего импульса U3 триггер устанавливается в «1» состояние (Q=1), в результате чего ЕСТ=1 и каждый очередной тактирующий импульс генератора G будет увеличивать число N в счетчике ПДС на единицу. Импульсный сигнал Uвых появится на выходе Fвых проектируемого устройства после того, как число N станет равным числу Ny. При этом сигналом обратной связи с выхода Fвых ПДЧ на К -вход JK - триггера последний будет переведен в «0» -состояние и своим сигналом  =R=1 переведет в исходное состояние ПДЧ (N=0; ЕСТ=0).

=R=1 переведет в исходное состояние ПДЧ (N=0; ЕСТ=0).

Из изложенного выше следует, что в схеме рис. 10.56 между величиной Тзд и численным значением кода управления Ny имеет место следующая линейная зависимость:

Тзд=ТG*Nу

где Tg - период следования импульсов тактового генератора G.

2.Анализ работы схемы рис.10.56 показывает, что при ее работе с шагом ∆Тзд регулирования задержки импульсов, равным 0.1мкс

134

|

|

(∆Тзд=0,1мкс) период TG импульсных сигналов тактового генератора G и их частота fG должны быть равны соответственно;

Tg =∆Тзд=0,1мкс

|

|

3. Число Р возможных значений времени задержки Тзд, реализуемых проектируемым устройством, определяется из соотношения:

|

|

4. Количество двоичных разрядов n, необходимых дляотображения числа Р=256, равно

Таким образом, в ПДЧ проектируемого устройства рис.10.56 счетчик и цифровой компаратор (см. рис. 10.26. а) должны быть восьмиразрядными.

5. В серии КР1533 отсутствует 8 -разрядные ИМС счетчиков и цифровых компараторов. Поэтому для построения проектируемого устройства выбираем ИМС 4 -разрядных двоичных счетчиков КР1533ИЕ10 и цифровых компараторов КР1533СП1 с последующим каскадным их соединением для получения 8 -разрядного ПДЧ в составе данного устройства.

6. Электрическая схема проектируемого цифрового устройства регулируемой задержки импульсов приведена на рис.10.57. В ней использованы следующие ИМС: DD1-KP1533TB15; DD2, DD3-КР1533ИЕ10; DD4, DD5- КР1533СП1.

7. (Для самостоятельного решения). Постройте цифровое устройство регулируемой задержки импульсных сигналов, работающее в диапазоне значений Тзд от 0 до 100мкс с шагом регулирования задержки ∆Тзд, равным 0,1мкс.

136

Пример 7. Используя ИМС серии КР1554, постройте преобразователь 8 -разрядного параллельного двоичного кода в последовательный двоичный код, передаваемый в однопроводную линию связи с его выхода Fвых старшим (младшим) разрядом вперед. Порядок передачи разрядов 8 -разрядного слова, начиная со старшего, либо с младшего его разряда, определяется сигналами схемы управления (СУ). Сигнал завершения передачи последовательного 8 -разрядного слова должен формироваться на отдельном выходе преобразователя Fq.

Решение

1. Преобразование параллельного двоичного кода в последовательный может быть выполнено с помощью мультиплексора, содержащего N информационных входов D0,D1,...,Dm и один выход Fвых. В данном случае

имеем:

|

|

где n - число адресных входов мультиплексора.

Из полученных выше результатов следует, что для построения проектируемого преобразователя должен быть использован 8 -канальный мультиплексор, реализующий последовательную адресуемую коммутацию данных D0,D1,...,D7 с его информационных входов на выход Fвых. При этом коммутация вида (N→l)=(8→l) выполняется под управлением 3 -разрядных адресных кодов {A2A1A0}.

2. Серия ИМС КР1554 не содержит 8 -канальных мультиплексоров. Поэтому переведем в режим работы 8 -канального мультиплексора ИМС КР1554КП12, которая содержит два четырехканальных мультиплексора с выходом на три состояния, имеющих общие адресные входы выбора данных (см. рис. 10.58).

3. Проектируемый преобразователь должен обеспечить реализацию одного из двух следующих режимов формирования последовательных кодов данных {D0,D1,...,D7}:

• При передаче данных в последовательную линию младшим разрядом вперед в первом такте на выходе Fвых преобразователя должен формироваться разряд данных D0, во втором такте - разряд D1,..., в восьмом такте - разряд D7.

137

| Ласледо-вательный код данных {»„...,!>„] |

| вательныи вод данных {D1S„..,D0} |

• При передаче данных старшим разрядом вперед в первом такте на выходе Fвых формируется D7 ; во втором такте – D6,..., в восьмом такте – D0.

Из этого вытекает, что в проектируемой схеме должна быть предусмотрена возможность реверсирования направления перебора адресов опрашиваемых информационных входов:

• При прямом порядке перебора адресов кодовые комбинации на адресных входах {А2А1А0} должны реализоваться в следующем порядке: {000}; {001}; {010}; {011}; {100}; {101}; {110} и {111}. Далее цикл адресации повторяется.

• При обратном порядке перебора адресов комбинации {A2A1A0} должны реализоваться в следующем порядке: {111}; {110}; {101}; {100}; {011}; {010}; {001}; {000}, после чего цикл адресации повторяется.

4. С учетом изложенного выше в п.3 для адресации в циклическом режиме опрашиваемых информационных входов D0,D1,...,D7 мультиплексора применим реверсивный четырехразрядный двоичный счетчик КР1554ИЕ7 с раздельными тактовыми входами прямого и обратного счета, которые соединим с выходами схемы управления (СУ). При этом в указанной адресации участвуют только три младших разряда счетчика Q2,Q1 и Q0.

В исходном состоянии в счетчик должно быть загружено четырехразрядное число {Q3Q2Q1Q0}={1000}. Тогда при реализации по команде СУ прямого счета будет выполняться преобразование параллельного двоичного кода в последовательный с передачей его в последовательную линию младшим разрядом вперед. Соответственно при реализации обратного счета передача кода будет выполняться старшим разрядом вперед (см. таблицу 10.20).

5. Электрическая схема проектируемого преобразователя приведена на рис. 10.58. В ней применены следующие ИМС: DD1-KP1554ИE7; DD2-КР1554ЛП5; DD3-KP1554ЛН1; DD4-KP1554KП12. Для формирования сигнала Fq завершения передачи последовательного 8 -разрядного слова выходы прямого переноса  и обратного переноса

и обратного переноса  счетчика должны быть объединены логической функцией равнозначности:

счетчика должны быть объединены логической функцией равнозначности:

Fq=

138

|

|

Рис.10.59

139

Таблица 10.20.

|

|

Сигнал Fq используется в схеме рис.10.58 также для инициализации загрузки в счетчик DD1 числа {1000}, необходимого для перевода преобразователя в исходное состояние. Кроме того, сигнал Fq поступает по цепи обратной связи на вход схемы управления, обеспечивая таким образом идентификацию моментов завершения передачи предыдущего слова и начала следующего 8 -разрядного последовательного слова.

Пример 8. Используя ИМС серии КР1533, постройте преобразователь параллельного 16 -разрядного двоичного цифрового кода {D15D14 ...D1D0} в последовательный двоичный цифровой код, формируемый на выходе преобразователя Fвых младшим разрядом D0 вперед. При этом на других выходах преобразователя Fq и Fe должны формироваться следующие сигналы:

• Сигнал Fq завершения передачи 16 -разрядного последовательного двоичного слова

|

|

• Сигнал Fе проверки на четность суммы единиц во входном параллельном коде {D15D14...D1Do}. Где

140

|

|

Решение

1. Анализ условий задачи и результатов решения предыдущего примера показывает, что проектируемый преобразователь может быть выполнен в соответствии со структурной схемой, приведенной на рис.10.59.

2. Построение 16 -канального мультиплексора (16→1) для схемы преобразователя выполним на основе 8 -каналышх селекторов-мультиплексоров с тремя состояниями на выходе КР1533КП15. При этом входы EZ управления установкой выходов мультиплексоров в третье состояние (см. рис. 10.60) используем в качестве дополнительных адресных входов выбора.

3. Циклическую последовательную адресацию информационных входов мультиплексора реализуем с помощью 4 -разрядного двоичного суммирующего счетчика КР1533ИЕ10, тактовый вход которого С соединен с выходом автогенератора G, а его информационные выходы {Q3, Q2, Q1, Q0} соединены с адресными входами {А3А2А1А0} мультиплексора. Так как модуль счета К счетчика КР1533ИЕ10 равен шестнадцати (К=16), го выход переноса CR может быть использован в качестве выхода Fq, сигнализирующего о завершении передачи преобразователем 16 -разрядного последовательного слова данных {D15D14...D0}.

CR=Fq

4. Шестнадцатиразрядную схему контроля четности построим на основе двух 9 -разрядных схем КР1533ИП5, выходы четности которых объединим с помощью логического элемента «Исключающее ИЛИ»

КР1533ЛП5 (см. рис. 10.60):

Fe= Fe1⊕Fe2

где Fe1, Fe2 - выходные сигналы четности первой и второй ИМС контроля четности.

5. Электрическая схема проектируемого преобразователя приведена на рис.10.60. Для ее построения применены следующие ИМС серии КР1533:

141

|

|

Рис.10.60

142

DDl-КР1533ИЕ10; DD2, DD3-KP1533KП15; DD4-KP1533ЛH1, DD5, DD6-KP1533ИП5; DD7-KP1533ЛП5.

6. (Для самостоятельного решения). Спроектированный выше преобразователь рис.10.60 осуществляет преобразование параллельного 16- разрядного двоичного кода в последовательный 16 -разрядный двоичный код с передачей его в последовательную линию связи младшим разрядом D0 вперед. Перестройте схему рис.10.60 таким образом, чтобы передача 16 -разрядного последовательного кода выполнялась старшим разрядом D15 вперед.

Пример 9. Разработайте цифровое устройство управления (ЦУУ) 16 -канальным аналоговым коммутатором К543КН2. ЦУУ должно обеспечить адресный опрос аналоговых каналов коммутатора {D0, D1,…,D15} в следующем циклическом режиме их коммутации: вначале каналы коммутируются в прямом порядке – D0, D1,…,D15, а затем в обратном

порядке – D15, D14, D13,…,D0. Продолжительность цикла коммутации Тц составляет 500мкс. ЦУУдолжно быть выполнено на основе КМОП (ТТЛШ) ИМС серии КР1554(КР1533).

Решение

1. ИМС К543КН2 представляет собой 16 -канальный двухгрупповой аналоговый коммутатор с управлением параллельным двоичным цифровым кодом. Анализ работы ИМС К543КН2 показывает, что проектируемое цифровое устройство управления может быть выполнено в соответствии со структурной схемой, приведенной на рис.10.61. Где: SWT - коммутатор К543КН2; RCT - реверсивный 4 -разрядный двоичный счетчик; СУ - схема управления тактированием SWT и направлением счета счетчика RCT.

2. Электрическая схема проектируемого цифрового устройства управления, построенная в соответствии со структурной схемой рис.10.61, приведена на рис. 10.62.

3. В схеме рис. 10.62. 16 -канальный аналоговый коммутатор DD1 переведен в режим адресного опроса аналоговых каналов {D0, D1,...D15} посредством подачи на его входы управления адресным и последовательным опросом SED1 и SED2 следующих сигналов:

SED1=1; SED2=0.

143

|

|

Рис 10.61

4. Реверсивный счетчик DD2 схемы рис. 10.62 в режиме прямого счет! обеспечивает адресацию прямого порядка опроса аналоговых каналов; при обратном счете - адресацию обратного порядка их опроса. Такил образом, в проектируемом ЦУУ реверсирование направления опрос; информационных каналов осуществляется путем реверсированш направления счета счетчика DD2.

5. Управление чередованием прямого и обратного порядка опросг информационных каналов в пределах цикла Тц реализует схема управления, включающая D - триггер DD3.1, работающий в режиме асинхронного Т -триггера, логические элементы И-НЕ DD4.1, DD4.2 и генератор G. Изменение направления опроса каналов происходит при опрокидывании триггера DD3.1 в состояние, инверсное предыдущему его состоянию, При этом указанное опрокидывание триггера вызывает сигнал,

144

|

|

145

|

|

поступающий по цепи обратной связи на его вход С с выхода переноса CR счетчика DD2. Где:

CR=  ⊕

⊕

6. Тактирование работы коммутатора и схемы управления осуществляет генератор G. Частота fG, период TG, длительность импульса tи, длительность паузы tп и скважность Q импульсных сигналов генератора G определяется следующим образом:

|

|

где NT – число тактов в цикле

|

|

Предельно допустимые режимы эксплуатации ИМС К543КН2 определяют допустимую длительность тактовых импульсов в пределах 0,3,...,5 мкс при максимальной частоте тактовых имульсов  400кГц. С учетом этого принимаем tи=4,5мкс.

400кГц. С учетом этого принимаем tи=4,5мкс.

Тогда

tп = TG- tи=15,625-4,5=l l,125мкс

|

|

7. Для построения проектируемой схемы ЦУУ на основе КМОП ИМС серии КР1554 в схеме рис.10.62 могут быть использованы следующие микросхемы: DD1-K543KH2; DD2-KP1554ИE7; DD3-KP1554TM2; DD4-КР1554ЛАЗ; DD5-KP1554ЛП5

8. Аналогично этому при построении проектируемого ЦУУ на основе ТТЛШ ИМС серии КР1533 в схеме рис.10.62 могут быть использованы следующие микросхемы: DD1-KP543KH2; DD2-KP1533ИE7; DD3-КР1533ТМ2; DD4-KP1533ЛАЗ; DD5-KP1533ЛП5.

146

9.Для обеспечения надежной работы ИМС коммутатора К543КН2 под управлением спроектированного цифрового устройства управления рис.10.62 на выводы (42), (14) и (21) ИМС должны быть поданы от источников питания Uп1, Uп2 и Uп3 следующие значения напряжения: Uп1= -15В; Uп2=+5В и Uп3=+12В.

Заметим, что в данном случае независимо от построения ЦУУ на основе КМОП или ТТЛШ ИМС напряжение питания Uп2 должно быть равно +5В. Это обусловлено тем, что ИМС серий КР1554 и КР1533 имеют пятивольтовое питание ЕП=+5В и, таким образом, их выходные управляющие сигналы «0» и «1» формируются в соответствии с указанным напряжением питания Еп.

10. (Для самостоятельного решения). На основе ИМС 16 -канального аналогового коммутатора К733КН2-2 постройте коммутатор и его цифровое устройство управления, обеспечивающее работу коммутатора в следующих режимах:

· В режиме адресного опроса аналоговых информационных каналов с произвольным порядком их адресации, задаваемым внешним устройством.

· В режиме последовательного опроса аналоговых информационных каналов.

· В режиме «челнокового» опроса анологовых информационных каналов, включающем их циклическую коммутацию в прчмом и обратном порядке соответственно.

Пример 10. Разработайте структурную схему устройства проверки на достоверность (УПД) аналоговых информационных сигналов, коммутируемых 16 -канальньш аналоговым коммутатором. В качестве критерия достоверности примите нахождение величины Uвых указанных сигналов на выходе коммутатора в диапазоне:

Umin  Uвых

Uвых  Umax

Umax

где Umin; Umax - нижняя и верхняя границы поля допуска.

Каждая коммутация недостоверного сигналя должна регистрироваться в проектируемом УПД с параллельной регистрацией номера информационного канала, при подключении которого произошел сбой. После того как число сбоев Nсб.j, зарегистрированное в j -ом канале, станет равным пороговому числу критерия неисправности Nкн.j

Ncб.j  Nкн.j

Nкн.j

j - ый какал должен быть отключен с целью исключения дальнейшего попадания недостоверной информации в аппаратуру обработки.

Опишите алгоритм функционирования спроектированного вами УПД для случая работы коммутатора в режиме адресного опроса каналов с их адресацией от схемы управления (СУ).

Решение

1. Один из возможных вариантов построения структурной схемы проектируемого устройства УПД представлен на рис. 10.63. Где SWT -шестнадцатиканальный коммутатор; Кл.1, Kл.2 - аналоговые ключи, управляемые сигналами V1 и V2; ФИ1, ФИ2 - формирователи импульсов, срабатывающие при переключении сигнала 0  1 на выходе компораторов нижней и верхней границ допуска соответственно; М - оперативное запоминающее устройство; СТ2 -двоичный 4 -разрядный счетчик с трехстабильными выходами; ЦСС - цифровая схема сравнения двоичных цифровых кодов.

1 на выходе компораторов нижней и верхней границ допуска соответственно; М - оперативное запоминающее устройство; СТ2 -двоичный 4 -разрядный счетчик с трехстабильными выходами; ЦСС - цифровая схема сравнения двоичных цифровых кодов.

2. Устройство рис. 10.63 реализует следующий алгоритм функционирования. Адрес опрашиваемого информационного канала {А3А2А1А0} поступает от СУ на коммутатор SWT и на оперативное запоминающее устройство М. Для коммутатора SWT адрес {А3А2А1Ао} является адресом опрашиваемого j-гo информационного канал, аналоговый сигнал которого Uвых должен быть представлен на выходе

148

коммутатора, а для ОЗУ указанный адрес является адресом ячейки памяти, в которой хранится информация о количестве сбоев N‾сб.j, имевших место при предшествующих опросах j - го информационного канала.

|

|

Одновременно с подачей адреса {А3А2А1А0} схема управления формирует на входе  ОЗУ и на входах

ОЗУ и на входах  и

и  счетчика СТ2 «нулевые»

счетчика СТ2 «нулевые»

149

логические сигналы:  =0;

=0;  =0;

=0;  =0. Вследствие этого выходы счетчика {Qo,Q1,Q2,Q3} переводятся в Z -состояние и выполняется параллельная загрузка в него числа N‾сб.j, считываемого с выходов {q0q1q2q3} озу.

=0. Вследствие этого выходы счетчика {Qo,Q1,Q2,Q3} переводятся в Z -состояние и выполняется параллельная загрузка в него числа N‾сб.j, считываемого с выходов {q0q1q2q3} озу.

По завершении загрузки в счетчик числа сх N‾сб.j схема упарвления реализует сигнал  =1 и двоичное число N‾сб.j с его выходов {Q0,Q1,Q2,Q3} поступает на входы {а0а1а2а3} цифровой схемы сравнения (ЦСС), где это число сравнивается с двоичным числом Nkh.j. формируемым на входах {в0в1в2в3} ЦСС задатчиком уставок критерия неисправности j -гo канала. В том случае, когда имеет место

=1 и двоичное число N‾сб.j с его выходов {Q0,Q1,Q2,Q3} поступает на входы {а0а1а2а3} цифровой схемы сравнения (ЦСС), где это число сравнивается с двоичным числом Nkh.j. формируемым на входах {в0в1в2в3} ЦСС задатчиком уставок критерия неисправности j -гo канала. В том случае, когда имеет место

N‾сб.j  Nkн.j,

Nkн.j,

на входы V1 и V 2 ключей Кл.1 и Кл.2 поступает сигнал Fвых = 0, вследствие чего указанные ключи заперты (разомкнуты) и аналоговый сигнал Uвых, закоммутированный коммутатором SWT, не поступает ни на компараторы КU, Kd, ни в аппаратуру обработки информации.

Если имеет место соотношение

N‾сб.j  Nкн.J,

Nкн.J,

то сигналом Fвых= l ключи Кл.1, Кл.2 открываются и закоммутированный аналоговый информационный сигнал Uвых поступает на компараторы КU, Kd, где анализируется находится ли его величина в пределах поля допуска. При обнаружении сбоя очередной импульс формирователя ФИ1,2 поступает на счетный вход счетчика, в результате чего, зарегистрированное в нем ранее число N‾сб.j увеличивается на 1.

N+сб.j = N‾сб.j

Далее число N+сб.j записывается в ячейку памяти ОЗУ с j - адресом и схема управления формирует адрес следующего опрашиваемого информационного канала, сигналы которого проходят проверку на достоверность (на допустимость аналогично описанному выше.

Пример 11. Используя ТТЛШ интегральные микросхемы и совместимые с ними ИМС, спроектируйте электрическую схему блока А2 устройства, структурная схема которого приведена на рис. 10.63. Выполните необходимые расчеты с учетом того, что величина напряжения UBbIX, поступающего с коммутатора, находится в диапазоне от Umin = -5B до Umax=+10B. Допустимое смещение нуля не должно

150

превышать 10мВ. Время срабатывания блока А2 при обнаружении сбоя Tср, не должно превышать 0,5мкс.

Решение

1. Анализ исходных данных и алгоритма функционирования схемы рис.10.63, описанного выше в примере 10, показывает, что для построения проектируемого блока А2 могут быть применены следующие ИМС:

• Сдвоенный компаратор напряжения К521СА6, который имеет следующие значения величин его электрических параметров:

Напряжение питания Uп1=12B  25%

25%

Uп2 =-12

Uп3= 5B  l0

l0

Входное напряжение Uвх =  5B

5B

Выходное напряжение U°вых

2020-08-05

2020-08-05 594

594