Регистры строятся на основе триггеров, их число соответствует количеству разрядов в обрабатываемой двоичной информации.

Регистры предназначены для хранения и обработки информации.

Основные теоретические положения

Регистры,

ЛЕКЦИЯ 14. Регистры, счетчики

Сумматор является основным элементом Арифметико-логического устройства (АЛУ) микропроцессора и выполняет все арифметические операции (сумма, разность, умножение, деление и т.д.).

Они выполняют преобразование из параллельного кода в последовательный код и обратно, используются в арифметических и логических операциях.

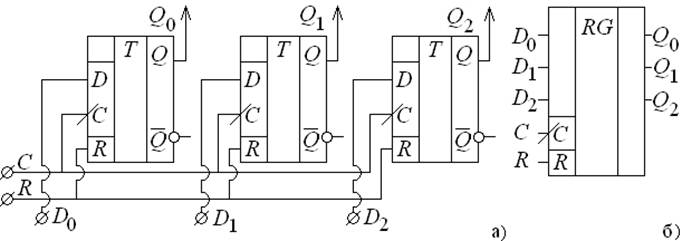

В данных регистрах запись информации производится параллельным кодом одновременно во всех разрядах. Параллельные регистры применяются для хранения информации, например, в микропроцессорах. Эти регистры можно реализовать практически на всех видах триггеров. Чаще всего используются D -триггеры, как наиболее простые устройства (рис. 1).

Рис. 1 Трехразрядный параллельный регистр:

а – функциональная схема; б – обозначение регистра

Входы D 0, D 1, D 2 служат для записи информации по переднему фронту тактового сигнала C. Выходные сигналы Q 0, Q 1, Q 2.

К перечисленным выводам регистров обычно подключаются логические элементы для разрешения записи и считывания информации.

Вход R служит для приоритетного асинхронного стирания данных во всех триггерах, обычно перед началом работы.

Пример регистра в интегральном исполнении: микросхема К555ИР23 восьмиразрядный параллельный регистр с динамическим управлением.

2014-02-02

2014-02-02 757

757