Обзор

Для хранения программ и данных процессоры ADSP_2106x имеют большой объем двухпортовой памяти, расположенной на кристалле. Память делится на два блока, которые называются блок 0 и блок 1. Объем памяти, доступной в процессорах ADSP_2106x, приведен ниже:

Характеристики SRAM ADSP_21060 ADSP_21062 ADSP_21061

Полный объем 4 Мбит 2 Мбит 1 Мбит

Объем блока 2 Мбит 1 Мбит 0.5 Мбит

число 48_разрядных слов

на блок 40 Кслов 20 Кслов 8 Кслов

число 32_разрядных слов

на блок 64 Кслова 32 Кслова 16 Кслов

число 16_разрядных слов

на блок 128 Кслов 64 Кслова 32 Кслова

Через внешний порт процессора ADSP_2106x можно адресовать до 4 гигаслов

дополнительной памяти, находящейся вне кристалла. 32_разрядные слова используются для представления данных с плавающей точкой одиночной точности стандарта IEEE. 48_разрядные слова содержат команды или 40_разрядные данные с плавающей точкой повышенной точности.

Кроме того, для представления целочисленных или дробных данных ADSP_2106х поддерживает формат 16_разрядных коротких слов. В каждом процессоре ADSP_2106х память соединяется с другими функциональными устройствами через три внутренние шины: шину памяти

|

|

|

программы (PM), шину памяти данных (DM), шину ввода_вывода (I/O). Шина PM и шина DM совместно используют один порт памяти, а шина I/O – другой. Внутренние шины PM и DM управляются ядром процессора, шина I/O управляется устройством ввода_вывода (IOP), расположенным на кристалле ADSP_2106x. Шина I/O позволяет осуществлять параллельную передачу данных между любым блоком памяти и портами связи ADSP_2106х (линк_портами, последовательными портами и внешним портом).

При такой двухпортовой структуре обращения к внутренней памяти ядра процессора и устройства ввода_вывода осуществляются независимо по отношению друг к другу. В одном цикле к каждому блоку памяти могут обращаться и ядро процессора, и устройство ввода_вывода, причем когда ядро процессора и устройство ввода_вывода обращаются к одному и тому же блоку, то дополнительных циклов не требуется.

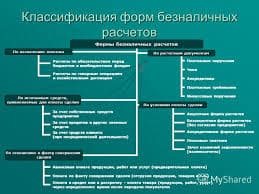

Рис. 5.1. Блок-схема ADSP-2106x

Ядро процессора и устройство ввода_вывода имеют доступ к внешним шинам (DATA47_0, ADDR31_0) через внешний порт ADSP_2106х. Внешний порт обеспечивает доступ к памяти, размещенной вне кристалла, и к периферийным устройствам. Через него можно обращаться к внутренней памяти других ADSP_ 2106х, соединенных в многопроцессорную систему. Схема соединения с общей

шиной позволяет реализовывать одно объединенное адресное пространство, в котором могут храниться и код, и данные.

Внешняя память может быть 16_, 32_ или 48_разрядная; контроллер прямого

доступа в память (DMA) автоматически упаковывает внешние данные в слова соответствующей разрядности: 48_разрядные команды или 32_разрядные данные. Заметим, что внутренняя память разделена на два блока, называемые блок 0 и блок 1, а внешнее пространство памяти разделено на четыре банка.

2015-01-30

2015-01-30 389

389