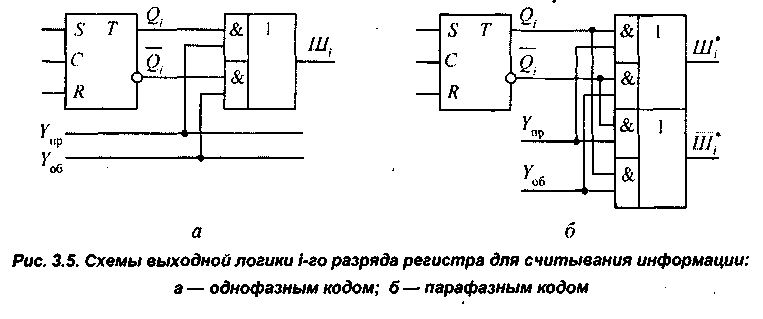

Информация, хранимая в регистрах, может передаваться во внешние схемы однофазным или парафазным способом в прямом или обратном коде. Для реализации микроопераций считывания к выходам каждого триггера подключаются комбинационные схемы, образующие выходную логику регистра.

Схемы выходной логики строятся на основе следующих поразрядных логических уравнений:

• для считывания однофазным прямым или обратным кодом

Шi = Yпр Qi v Yоб  (5.3)

(5.3)

• для считывания парафазным прямым или обратным кодом

Шi = YnpQi v Yпр  ; Шi = Yo6

; Шi = Yo6  v Yo6Qi (5.4)

v Yo6Qi (5.4)

где Yпр и Yo6 — управляющие сигналы выдачи соответственно прямого или обратного кода;

Qi и Qi — прямое и инверсное значение, выхода r'-го разряда регистра;

Шi — разряд однофазной шины данных;

Шi и Шi — разряды парафазной шины данных.

Очевидно, что управляющие сигналы Yпр и Yоб не должны совпадать во времени.

Схемы выходной логики для i-го разряда на основе уравнений (5.3) и (5.4) показаны на рис. 5.5.

Рисунок 5.5-Схемы выходной логики i-разряда для считывания информации:

а) однофазным кодом; б) парофазным кодом

2015-03-22

2015-03-22 877

877