Разработку структурной электрической схемы кодера ССК следует выполнять с определения основных функций кодера, к которым следует отнести [1–3, 5]:

– разделение символов входного информационного потока на k0 ≥ 2 информационных подпотоков – I1(D), I2(D), …, Ik0(D); при k0=1 входной информационный поток не делится на подпотоки;

– формирование проверочных (контрольных) символов Рпер.(D) из входных информационных символов;

– объединение символов k0 информационных подпотоков и проверочных символов (n0 – k0) подпотоков в кодовый поток или в поток кодовых символов  .

.

Для реализации данных функций необходимо определить функциональные узлы (блоки) кодера и далее объединить их в структурную электрическую схему. После этого дать краткое описание работы кодера.

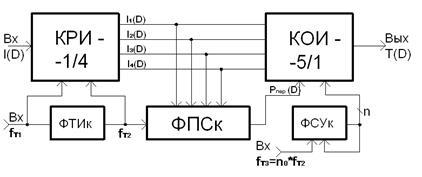

Пример 4. Для выбранного ССК с R= k0/n0 = 4/5 основными функциональными узлами являются:

КРИ-1/4 – коммутатор разделения символов входного информационного потока I(D) на k0 = 4 информационных подпотоков;

ФПСк – формирователь проверочных символов кодера;

КОИ-n0/1 или КОИ-5/1 – коммутатор объединения информации или символов k0 = 4 информационных и одного (n0 – k0) = (5 – 4) = 1 проверочного подпотока в единый кодовый поток.

Для нормального функционирования основных блоков кодера используются соответствующие ФТИк и ФСУк.

В соответствии с [1-3] структурная электрическая схема кодера ССК будет иметь следующее построение (рисунок 1).

Кодер ССК работает следующим образом. Символы входного информационного потока I(D) разделяются в КРИ-1/4 на четыре подпотока – I1(D),…, I4(D). Информационные символы данных подпотоков поступают одновременно на соответствующие входы КОИ-5/1 и ФПСк. В ФПСк из символов информационных подпотоков формируются проверочные символы Рпер.(D) по алгоритму:  , j = 1,2,…,k0.

, j = 1,2,…,k0.

Сформированные проверочные символы поступают на соответствующий вход КОИ-5/1, который объединяет символы информационных подпотоков I1(D),…, I4(D) и символы проверочного подпотока в единый поток кодовых символов T(D), поступающих далее на вход устройства преобразования сигналов (УПС) или модема ДКС.

Рисунок 1 – Структурная электрическая схема кодера ССК

2015-04-30

2015-04-30 658

658