Одним из передовых производителей ПЛИС является фирма «Altera». Она предлагает два достаточно развитых пакета программ для проектирования устройств на ПЛИС: MAX+plus II и Quartus II. Так же фирма «Altera» предлагает бесплатные версии этих САПР: MAX+plus II BASELINE и Quartus II Web Edition. Каждый САПР поддерживает все этапы проектирования: Ввод проекта, Компиляция, Верификация и Программирование. Каждый САПР имеет Tutorial (Самоучитель), который устанавливается при инсталляции пакета. Tutorial состоит из занятий, в ходе которых проходится весь цикл проектирования от ввода проекта до программирования микросхем. Ограничениями являются количество поддерживаемых микросхем и некоторые функции для Quartus II. При инсталляции также устанавливаются файлы, описывающие проект так, что в ходе изучения Tutorial можно пропускать отдельные занятия и использовать готовые файлы. Например, можно пропустить "Ввод проекта" и перейти к "Компиляции" проекта, используя готовые файлы.

САПР MAX+plus II является более простым в освоении по сравнению с Quartus II. Он поддерживает семейства MAX, FLEX и ACEX, которые содержат микросхемы с 5В питанием и количеством функциональных преобразователей от 32 до 4992 и имеет меньшее количество настроек. Этот САПР фирма Altera не развивает и рекомендует переходить на Quartus II.

САПР Quartus II является основным. Фирма Altera активно его развивает. Он поддерживает все новые семейства микросхем и обладает особенностями, которых нет в MAX+plus II. Несмотря на это в данной лабораторной работе рассматривается система проектирования MAX+plus II, так как она проще в изучении, имеет все необходимые средства для разработки и дает фундаментальные знания и навыки проектирования устройств, которые позже могут быть применены в боле сложных САПР.

4.3 Система MAX+Plus II

САПР MAX+plus II (Multiple Array Matrix Programmable Logic User) представляет собой архитектурно-независимую среду проектирования, которая легко приспосабливается к конкретным проектным требованиям и может работать на различных компьютерных платформах.

MAX+plus II предоставляет полный спектр возможностей для проектирования цифрового устройства: различные способы ввода проекта, логический синтез, компиляцию с заданными временными ограничениями, функциональное и временное моделирование, разделение проекта на части и моделирование проекта, выполненного на нескольких микросхемах, временной анализ, автоматическое определение ошибок, программирование и верификацию микросхем. Так же он позволяет вводить и сохранять проекты в виде файлов AHDL (язык описания аппаратуры фирмы Atera), EDIF, Verilog HDL, VHDL, OrCAD. MAX+plus II может использовать netlist файлы фирмы Xilinx для ввода проекта, может создавать выходные SDF (Standard Delay Format) файлы для обеспечения удобного интерфейса с другими САПР промышленного стандарта CAE.

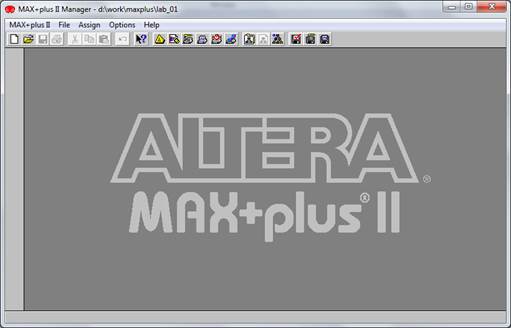

Ниже представлено главное окно программы (рис. 8), оно имеет стандартный интерфейс Windows-приложений. В заголовке окна программы указывается имя и путь последнего проекта, с которым велась работа.

|

Рисунок 8. Главное окно программы MAX+plus II.

В состав пакета MAX+PLUS II входят следующие связанные между собой приложения, реализующие все этапы разработки цифровых устройств на ПЛИС фирмы ALTERA:

1) Graphic Editor - графический редактор, предназначен для ввода проекта в виде схемы соединений символов элементов, извлекаемых из стандартных библиотек пакета либо из библиотеки пользователя.

2) Symbol Editor - символьный редактор позволяет редактировать существующие символы и создавать новые. Любой откомпилированный проект может быть свёрнут в символ, помещён в библиотеку символов и использован как элемент в любом другом проекте.

3) Text Editor - текстовый редактор является инструментом для создания текстовых файлов проекта на языках описания аппаратуры: AHDL (.tdj), VHDL (.vhd), Verilog HDL (.v). В этом текстовом редакторе можно работать также с произвольным файлом формата ASCII.

4) Waveform Editor - редактор временных диаграмм (сигнальный редактор), который выполняет двойную функцию: на этапе ввода обеспечивает ввод логики проекта в виде диаграмм (эпюр) состояний входов и выходов, а на этапе моделирования обеспечивает ввод диаграмм тестовых (эталонных) входных состояний моделируемого устройства и задание перечня тестируемых выходов.

5) Floorplan Editor - редактор связей, позволяет на плане расположения основных логических элементов вручную распределять выводы ПЛИС (закреплять выводы за конкретными входными и выходными сигналами) и перераспределять внутренние ресурсы ПЛИ.

6) Timing Analyzer - приложение, обеспечивающее расчет временных задержек от каждого входа до каждого логически связанного с ним выхода.

2015-05-10

2015-05-10 2139

2139