TAP требует 4-х внешних контактов:

TAP требует 4-х внешних контактов:

1. TDI (Test Data Input)—контакт для получения последовательных данных. На этот контакт последовательно, бит-за-битом податься данные, которые затем интерпретируются схемой управления;

2. TDO (Test Data Output)—контакт вывода последовательных данных. С этого контакта ведущее устройство последовательно считывает данные из БИС (например результат тестовых операций);

3. TCK (Test Clock Input)—контакт сигнала синхронизации обмена;

4. TMS (Test Mode Select)—этот контакт управляет состоянием внутреннего автомата TAP. В частности с помощью этого контакта определяется что грузиться: команда или данные, а также определяться начало и конец загрузки;

· TRST (Test ReSeT)—сброс в начальное состояние контроллера внутреннего автомата TAP (не является обязательным для реализации).

Основные инструкции:

1. BYPASS: TDI и TDO подключены к регистру обхода. (обеспечивает задержки лишь в 1 такт).

2. EXTEST: Регистр BS Chain подключен к TDI и TDO и к внешним выводам микросхемы. (ядро изолировано от ячеек boundary scan).

3. IDCODE: На выходе TDO последовательно появляются разряды идентификатора микросхемы.

4. INTEST: Регистр BS Chain подключен к TDI и TDO и к внешним портам функционального ядра микросхемы. (порт связан с ячейкой, но отделен от контакта).

Можно выделить два важных режима или состояния TAP:

· Состояние загрузки команд;

· Состояние загрузки данных;

Режим работы определяется текущим состоянием встроенного в TAP конечного автомата.

Граф включает в себя 16 состояний. Переход от состояния к состоянию осуществляется по каждому переднему фронту TCK. Ветвь перехода зависит от текущего состояния сигнала TMS.

Начальным состоянием автомата является Test Logic Reset. После включения питания, ведущее устройство "не знает", в каком состоянии окажется автомат TAP тестируемого устройства. Необходим способ гарантированного перевода TAP в начальное состояние. Таких способов два:

1. Установить на TMS высокий уровень и подать 5 или более импульсов TCK. В этом услучае автомат окажеться в состоянии Test Logic Reset;

2. Если реализован контакт TRST то автомат можно сбросить импульсом на этом выводе;

Загрузки команды в регистра команды происходит в состоянии Shift-IR.

Загрузка данных происходит в заданный регистр данных происходит в состоянии Shift-DR.

Какой именно регистр данных будет выбран для обмена, определяется текущим содержимым регистра команды.

DR — действия происходят над данными, IR — соответственно над инструкциями.

Более подробное описание каждого состояния:

1. Test-Logic-Reset —сброс логики тестирования. В этом состоянии тестирующая логика отключается, регистр команды инициализируеться кодом команды BYPASS или кодом команды вывода идентификационного кода интегральной схемы (IDCODE);

2. Run Test\Idle —состояние ожидания или выполнения внутренних тестов. Это состояние используеться как промежуточное между операциями. Например, если загрузкой некоторой команды и данных, была инициализирована продолжительная тестовая процедура, то на время ее выполнения TAP следует перевести в это состояние;

3. Select-DR-Scan —промежуточное состояние автомата, позволяет попасть в ветвь автомата, связанную с загрузкой данных;

4. Select-IR-Scan —промежуточное состояние автомата, позволяет попасть в ветвь автомата, связанную с загрузкой команды;

5. Capture-DR —это состояние подготовки данных к обмену. Данные, которые должны быть переданы ведущему устройству, загружаются в соответствующий регистр данных контроллера JTAG;

6. Shift-DR —в этом состоянии регистр данных включается между выводами TDI и TDO. Данные, подготовленные для ведущего устройства (результат текущей команды загруженной в командный регистр) последовательно выдвигаются наружу, замещаясь данными, которые передаются ведущим устройством;

7. Exit1-DR, Exit2-DR, Exit1-IR, Exit2-IR —промежуточные состояния, не оказывают никакого влияния на состояние тестовой логики, предназначены для быстрого перехода в начальное состояние;

8. Pause-DR, Pause-IR —эти состояния, позволяют приостанавливать продвижение информации на произвольное количество тактов синхронизации (например, для выполнения каких либо действий в БИС с внешним тактированием);

9. Update-DR —это состояние, в котором вдвинутые данные "защелкиваються", в момент выхода из этого состояния тестовая логика приступает к соответствующей операции с использованием загруженных данных;

10. Capture-IR —фактически промежуточное состояние, не оказывает никакого влияния на состояние тестовой логики;

11. Shift-IR —в этом состоянии регистр команды включается между выводами TDI и TDO. Текущее содержимое регистра последовательно выдвигается наружу, замещаясь командой, которые передаваемой ведущим устройством;

12. Update-IR —состояние фиксации и активизации вдвинутой команды;

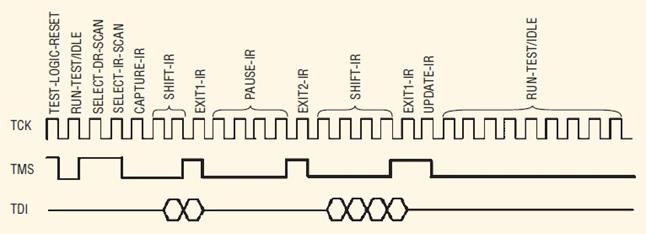

Диаграмма сигналов при выполнении переходов для загрузки команды:

Для управления необходимо знать разрядности всех сканируемых регистров:

1. bypass – одноразрядный сдвиговый регистр

2. ID – установлено в пасспорте

3. INST – 4-8

4. BS – 500-1000 (с ним работают EXTEST и INTEST)

ID – не перезаписываемый!

Регистр инструкций имеет теневой регистр (Shadow Instruction Register)

Пример:

Рассмотрим часть IR-Scan:

Выполняем IDCODE (101). Состояние Tap-контроллера – Test Logic Idle (после сброса, IR = 111). Внутренний регистр I/O будет записан в сдвиговый регистр с последовательным выводом на TDO.

1) TMS = 1, 2хТСК (подаем в течение 2ух тактов синхронизации), попадаем в состояние Select-IR Scan

2) TMS = 0, 1xTCK, попадаем в Capture-IR

3) TMS = 0, 1xTCK, срабатывает Shift-IR: TDI=IDCODE[0]=1, TDO << 1, IR = 111

4) TMS = 0, 1xTCK, срабатывает Shift-IR: TDI=IDCODE[1]=0, TDO << 1, IR = 011

5) TMS = 0, 1xTCK, TDO << 1, IR = 101

6) Выходим и обновляем регистр инструкций:

TMS = 1, 2xTCK => Exit1-IR, Update-IR

7) Инструкция записана:

TMS = 1, 1xTCK, Select-DR Scan

2015-05-30

2015-05-30 1356

1356