Используется технология EPROM-памяти со стиранием УФ-излучением и электрически стираемая EEPROM-память.

Используется технология EPROM-памяти со стиранием УФ-излучением и электрически стираемая EEPROM-память.

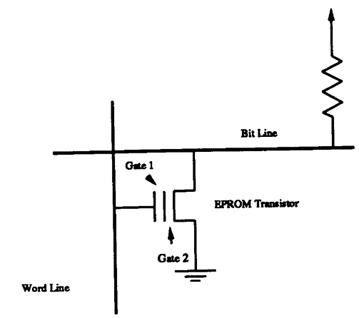

Программируемый переключатель, изображенный на рисунке 52.3, представляет собой транзистор, который может быть переведен в постоянно «выключенное» состояние. Данное состояние может быть достигнуто путем подачи высокого напряжения на gate 1 и сток транзистора. В этом случае возникнет заряд на gate 2 (плавающий затвор), который увеличит пороговое напряжение транзистора и транзистор закроется. Убрать этот заряд можно с помощью облучения плавающего затвора ультрафиолетовым излучением. Это приведет к уменьшению порогового напряжения на транзисторе и, как следствие, его нормальному функционированию.

Вместо того чтобы использовать EPROM транзистор напрямую в качестве программируемого переключателя, незапрограммированный транзистор используется для того чтобы заземлить ‘bit line’, в то время как ‘word line’ находится под напряжением. В то время как этот подход используется для создания соединения между ‘word’ и ‘bit’ линиями, его также можно применять в качестве проводной AND-логики.

EEPROM подход очень похож на EPROM за исключением того, что ликвидация заряда на плавающем затворе может быть выполнения электрическим путем без использования УФ-излучения. Это упрощает процесс пере программирования. Недостаток заключается в том, что EEPROM-ячейка в два раза больше EPROM ячейки.

Преимущества:

a) Как и в случае SRAM, данный подход отличается перепрогаммируемостью. Однако для его реализации не требуется дополнительная энергонезависимая память для программирования устройства при включении.

Недостатки:

a) Усложнение процесса обработки по сравнению с обычными CMOS-транзисторами.

b) Высокое сопротивление EPROM-транзистора в открытом состоянии.

c) Высокое энергопотребление.

Configurable Logic Blocks (CLB)

Configurable Logic Blocks (CLB)

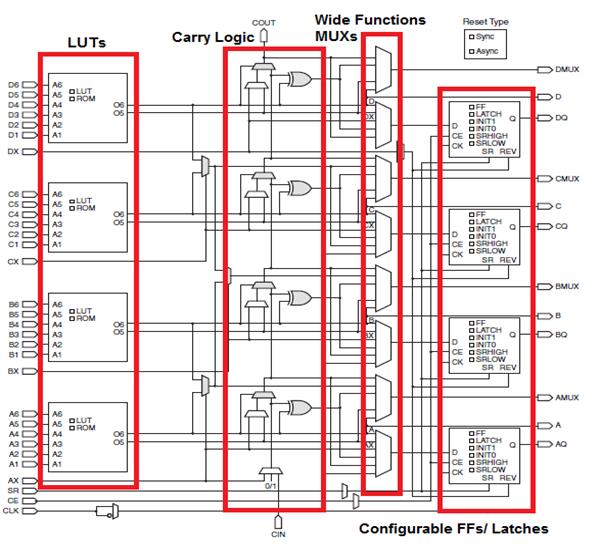

Логические блоки FPGA сильно отличаются в размерах и реализации. Двухтранзисторная логика, которая используется в FPGA от Crosspoint, может быть использована только как инвертер, однако она обладает очень маленьким размером, в то время как look-up table (LUT) логика, применяемая в FPGA от Xilinx, может реализовывать логическую функцию с пятью входами, но обладает значительно большим размером.

В данном случае хотелось бы рассмотреть именно логические элементы от Xilinx (по крайней мере с ними была найдена аналогия того материала, который рассказывался на лекции).

Каждый CLB блок разделен на две части, которые называются slice (SLICEM – реализация памяти, SLICEL – реализация логики). В свою очередь, каждый slice состоит из двух блоков (названия связаны с их координатным расположением в пределах slice). В каждом из них имеются линии ускоренного переноса. Каждый из них подключен к SB-блоками, к каналам прямых соединений с соседними CLB-блоками. SLICE представляет собой базовый конфигурационный узел. SLICEM может сконфигурирован для реализации функций сдвигового регистра (поэтому у него присутствуют дополнительные соединительные линии SHIFTIN/SHIFTOUT).

Каждый из slice состоит из

Каждый из slice состоит из

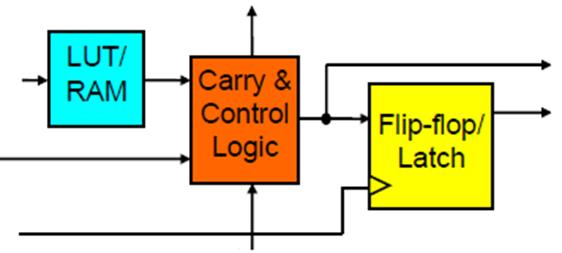

1)  Look-up tables (LUT), которые реализуют входы таблиц истинности логических функций. Некоторые FPGA могут использовать LUTs для реализации небольших RAM.

Look-up tables (LUT), которые реализуют входы таблиц истинности логических функций. Некоторые FPGA могут использовать LUTs для реализации небольших RAM.

2) Carry and Control logic.

a) Реализует быстрые арифметические операции (adders/substractors).

b) Могут быть также сконфигурированы для реализации дополнительных операций (Built-in-Self Test iterative-OR chain)

3) Элементы памяти (Memory elements)

a) Конфигурируемые Flip Flops (триггер)/Latches (Programmable clock edges, set/reset, and clock enable).

b) Эти элементы памяти зачастую могут быть реализованы как сдвиговые регистры.

Основой логического блока Xilinx является SRAM, функционирующий как LUT. Таблица истинности для K-входной логической функции хранится в

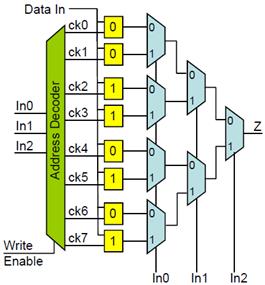

Основой логического блока Xilinx является SRAM, функционирующий как LUT. Таблица истинности для K-входной логической функции хранится в  RAM. Адресные линии SRAM работают как входы, а выход SRAM представляет собой выход логической функции.

RAM. Адресные линии SRAM работают как входы, а выход SRAM представляет собой выход логической функции.

1) Обычный LUT mode осуществляет операции чтения.

2) Адресные декодеры с установленным WE флагом генерируют тактовые импульсы защелкам (latches) для осуществления операций записи.

3) Небольшие RAMs могут быть использованы для получения RAMs большего размера.

Преимуществом LUTs является их высокая функциональность – K-входной LUT может реализовывать любую K-входную функцию, и таких функций существует  . Недостатком является то, что они становятся неприемлемо большими, если число входов больше чем 5, т.к. количество ячеек памяти, необходимых для LUT -

. Недостатком является то, что они становятся неприемлемо большими, если число входов больше чем 5, т.к. количество ячеек памяти, необходимых для LUT -  . Хотя число функций, которые могут быть реализованы с помощью LUT, очень быстро растет, эти дополнительные функции нечасто используются в проектируемой логике и их сложно использовать в средствах синтезирования логики. Поэтому

. Хотя число функций, которые могут быть реализованы с помощью LUT, очень быстро растет, эти дополнительные функции нечасто используются в проектируемой логике и их сложно использовать в средствах синтезирования логики. Поэтому  большие LUT используются нечасто.

большие LUT используются нечасто.

В общем, LUT может выполнять следующие функции:

2015-05-30

2015-05-30 725

725