36) Процессоры с Risc -архитектурой реализующие сокращенную систему команд

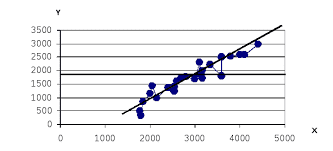

Процессоры с MIsc архитектурой реализуют минимальную систему команд (бытовая техника). На первый взгляд МК с Risc процессором должны иметь более высокую производительность по сравнению с Cics Мк при одной и той же же тактовой частоте внутренней магистрали. Однако на практике вопрос о производительности более сложен и неоднозначен. Во первых оценка производительности МК по времени выполнения команд различных систем (Risc и Cics) не совсем корректны. Обычно производительность Мп и Мк принято оценивать числом операций пересылки «регистр-регистр» Которые могут быть выполнены в течении одной сек. В МК с Cick процессором время выполнения операции «регистр-регистр» составляет то 1до 3 циклов что казалось бы уступает производительности МК с Rics процессором. Однако стремление к сокращению формата команд при сохранении ортогональности системы команд Risc процессора приводит к вынужденному ограничению числа доступных водной команде регистров.Во вторых оценки производительности МК по скорости пересылки «регистр-регистр» не учитывает особенностей конкретного реализуемого алгоритма управления.

Принцип построения процессора (СИСК, МИСК )

35) CISC (англ. Complex Instruction Set Computing) — концепция проектирования процессоров, которая характеризуется следующим набором свойств:

большим числом различных по формату и длине команд;

введением большого числа различных режимов адресации;

обладает сложной кодировкой инструкции.

Процессору с архитектурой CISC приходится иметь дело с более сложными инструкциями неодинаковой длины. Выполнение одиночной CISC-инструкции может происходить быстрее, однако обрабатывать несколько таких инструкций параллельно сложнее.

Облегчение отладки программ на ассемблере влечет за собой загромождение узлами микропроцессорного блока. Для повышения быстродействия следует увеличить тактовую частоту и степень интеграции, что вызывает необходимость совершенствования технологии и, как следствие, удорожание производства.

MiSc

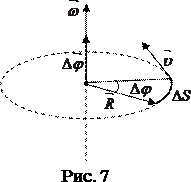

Увеличение разрядности процессоров привело к идее укладки нескольких команд в одно большое слово (связку, bound). Это позволило использовать возросшую производительность компьютера и его возможность обрабатывать одновременно несколько потоков данных. Кроме этого MISC использует стековую модель вычислительного устройства и основные команды работы со стеком языка Forth. MISC-принцип может лежать в основе микропрограммы выполнения Java- и.Net- программ, хотя по количеству используемых команд они нарушают принцип MISC.

Процессоры, образующие «компьютеры с минимальным набором команд» (MISC), как и процессоры RISC, характеризуются небольшим числом чаще всего встречающихся команд. Вместе с этим, принцип «очень длинных командных слов» (VLIW) обеспечивает выполнение группы непротиворечивых команд за один цикл работы процессора. Порядок выполнения команд распределяется таким образом, чтобы в максимальной степени загрузить маршруты, по которым проходят потоки данных. Таким образом архитектура MISC объединила вместе суперскалярную и VLIW-концепции. Компоненты процессора просты и работают на высоких частотах.

2015-05-30

2015-05-30 613

613