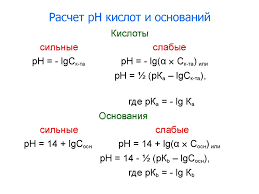

К типовым логическим устройствам ЭВМ относятся сумматоры, полусумматоры, триггеры, счетчики, шифраторы, дешифраторы. В этом разделе сделана попытка элементарного представления этих устройств на основании изученных элементов алгебры логики и теории конечных автоматов.

Сумматор в ЭВМ служит для суммирования чисел посредством поразрядного сложения. Он является активным узлом арифметико-логического устройства ЭВМ и выполняет сложение многозначных двоичных чисел. Сумматор представляет собой последовательное соединение одноразрядных двоичных сумматоров (рис. 7.25).

Рис. 7.25. Схема многоразрядного сумматора (Si – выход на разряд суммы, Pi – перенос в старший разряд,  ,

,  поразрядная двоичная запись суммируемых чисел)

поразрядная двоичная запись суммируемых чисел)

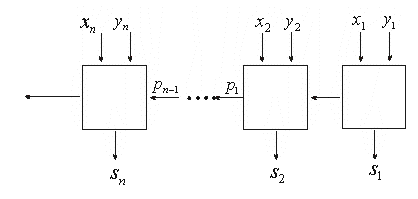

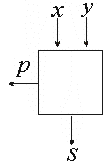

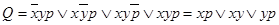

Очевидно, что сумматоры могут иметь два входа и два выхода (самый младший разряд), три входа и два выхода. Первые из них называется одноразрядным полусумматором.

|  |  |  |

а б

Рис. 7.26. Условное обозначение и таблица истинности одноразрядного полусумматора

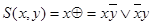

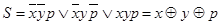

Из таблицы истинности полусумматора (рис. 7.26) видно, что:

.

.

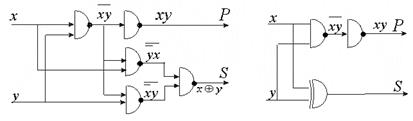

Тогда в базисе «и-не» и в схеме с использованием элемента « » для полусумматора получим функциональные схемы, представления на рис. 7.27.

» для полусумматора получим функциональные схемы, представления на рис. 7.27.

а б

Рис. 7.27. Реализации полусумматора на различных элементах

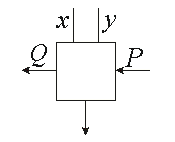

Для одноразрядного сумматора на три входа обозначения и таблица истинности приведена на рис. 7.28.

|  |  |  |  |

а б

Рис. 7.28. Условное обозначение (а) и таблица истинности (б) однообразного сумматора на три входа

На основании таблицы истинности запишем СД j функции

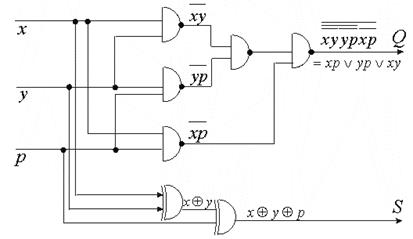

С использованием элементов «и-не» и « » реализация сумматора представлена на рис. 7.29.

» реализация сумматора представлена на рис. 7.29.

Рис. 7.29. Одна из возможных реализаций сумматора на три входа

Триггеры, логическую структуру которых мы рассмотрели в предыдущем разделе, используются в ЭВМ в качестве запоминающих ячеек. Они имеют два устойчивых состояния, в каждом из которых они находятся до тех пор, пока не поступит новый сигнал. Триггер – это устройство, которое может запоминать сигналы 0 и 1, демонстрировать их и, при необходимости, забывать. Функциональные схемы их представлены в разделе 7.3.

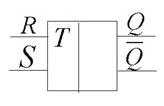

Учитывая эти схемы условные обозначения RS- и Т-триггеров представлены на рисунке 7.30.

Рис. 7.30. Условные обозначения RS- и Т-триггеров

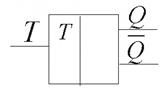

Поскольку под действием сигналов на входе Т-триггеры меняет свое состояние с 0 на 1 (или наоборот), то его называют счетным триггером. Число преобразований его состояний в точности равно числу поступивших сигналов.

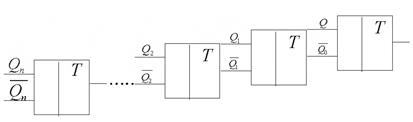

Тогда, если соединить выход каждого Т-триггера со входом следующего Т-триггера, то получится электронный счетчик, способный «запомнить» 2n поступивших сигналов, если использовать  триггеров.

триггеров.

Рис. 7.31. Схема электронного счетчика на Т-триггерах

Очевидно, что триггер запоминает один разряд двоичного числа. Для запоминания и демонстрации n-разрядного двоичного числа необходимо n параллельно соединенных триггеров, совокупность которых называется n-разрядным регистром.

Например, для запоминания одного байта потребуется 8 триггеров. Оперативная память ЭВМ конфигурируется в виде набора регистров и, как правило, один регистр образует одну ячейку памяти.

2015-06-10

2015-06-10 1934

1934