Способ №1

Иерархическое описание схемы в целом аналогично описанию, рассмотренному в работе №2. Отличие состоит в том, что добавляется описание подсхемы, а также в состав компонент могут входить более мелкие и простые компоненты.

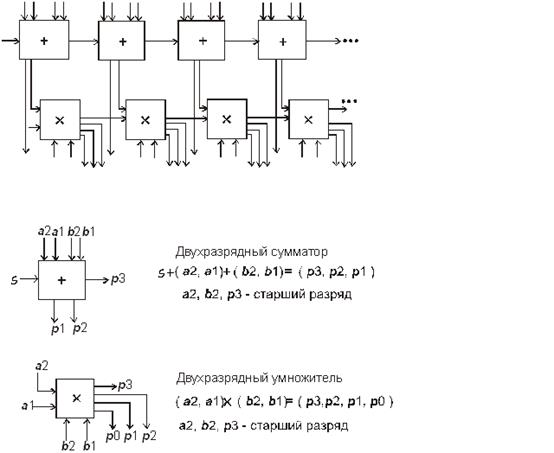

Получающаяся иерархическая структура представлена на рисунке 5.

|

∙ ∙ ∙

|

Рисунок 5. Иерархическая структура проекта для способа №1.

Для простоты следует ограничить количество значений каждого входного сигнала в тестирующей программе до 32.

Способ №2

В иерархической структуре проекта для способа №2, по сравнению со способом №1, отсутствует описание подсхемы, и все компоненты связаны напрямую с основной программой.

Рассмотрим особенности основной программы.

Вид оператора generic, который находится в описании интерфейса объекта entity (см. работу №1):

Entity имя объекта is

Generic (N:natural:= натуральное число);

Port (…);

End имя объекта;

N – настроечный параметр типа natural, которому присваивается конкретное значение (в нашем случае это будут значения от 2 до 5).

Тип сигнала BIT_VECTOR задаётся в описании интерфейса объекта следующим образом:

Entity имя объекта is

Port (имя сигнала: in BIT_VECTOR (K to L);

имя сигнала: out BIT_VECTOR (P downto Q));

End имя объекта;

Здесь K и Q – нижние границы диапазона, а L и P – верхние. В нашем случае нижняя граница всегда будет равна 0, а верхняя – N-1 или N.

Также тип данных BIT_VECTOR могут иметь и внутренние сигналы, объявляемые после ключевого слова signal в архитектурном теле объекта.

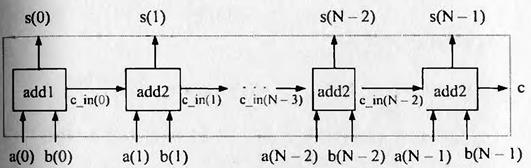

Рисунок 6. Схема N-разрядного сумматора.

Приведём небольшой пример описания N-разрядного сумматора (см. рисунок 6), иллюстрирующий все эти особенности, а также использование оператора generate.

Entity adder_N is

Generic ( N:natural:=4 );

Port ( a,b :in bit_vector ( 0 to N-1 );

s :out bit_vector ( 0 to N-1 );

c :out bit );

End adder_N;

Architecture func of adder_N is

Component add1

Port (b1,b2: in BIT;

c1,s1: out BIT);

end component;

component add2

port (c1,a1,a2: in BIT;

c2,s2: out BIT);

end component;

signal c_in: bit_vector (0 to N-1);

begin

add: for i in 0 to N-1 generate

first_bit: if (i=0) generate

first_cell: add1 port map (b1=>a(0), b2=>b(0), c1=>c_in(0),

s1=>s(0));

end generate first_bit;

middle_bit: if (i=>0) and (i<N-1) generate

middle_cell: add2 port map (c1=>c_in(i-1),a1=>a(i),

a2=>b(i),c2=>c_in(i),s2=>s(i));

end generate middle_bit;

end_bit: if (i=N-1) generate

end_cell: add2 port map (c1=>c_in(i-1),a1=>a(i),

a2=>b(i),c2=>c,s2=>s(i));

end generate end_bit;

end generate adder;

end func;

Описание регулярной структуры в варианте задания выполняется аналогично приведённому примеру.

В тестирующей программе также следует использовать операторы generate и generic, с помощью которых нужно задать все необходимые значения входных сигналов.

Вариант 1.

Способ №1

Способ №2

Вариант 2.

Способ №1

Способ №2

Вариант 3.

Способ №1

Способ №2

Вариант 4.

Способ №1

Способ №2

Вариант 5.

Способ №1

Способ №2

Вариант 6.

Способ №1

Способ №2

Вариант 7.

Способ №1

Способ №2

Вариант 8.

Способ №1

Способ №2

Вариант 9.

Способ №1

Способ №2

Вариант 10.

Способ №1

Способ №2

Вариант 11.

Способ №1

Способ №2

Вариант 12.

Способ №1

Способ №2

Вариант 13.

Способ №1

Способ №2

Вариант 14.

Способ №1

Способ №2

Вариант 15.

Способ №1 и 2

Вариант 16.

Способ №1 и 2

Вариант 17.

Способ №1 и 2

Вариант 18.

Способ №1 и 2

Вариант 19.

Способ №1 и 2

Вариант 20.

Способ №1 и 2

|

|

|

|

|

|

Вариант 21.

Способ №1 и 2

|

|

|

|

|

|

Вариант 22.

Способ №1 и 2

|

|

|

|

Вариант 23.

Способ №1 и 2

|

|

|

|

Вариант 24.

Способ №1 и 2

|

|

|

|

|

|

Вариант 25.

Способ №1 и 2

|

|

|

|

2015-06-05

2015-06-05 592

592