Мета роботи: вивчити принцип роботи лічильників - подільників частоти і регістрів.

Короткі теоретичні відомості

Лічильник – це функціональний вузол комп’ютера із пам’яттю, призначений для формування послідовних адрес команд програми (програмний лічильник), підрахунку кількості циклів при виконанні циклічних операцій (операції множення, ділення), в таймерах і ін. Вхідним сигналом лічильників є високостабільний періодичний сигнал (меандровий сигнал або послідовність коротких імпульсів). Функцією лічильників є створення біжучого значення паралельного двійкового коду, значення якого дорівнює біжучій кількості імпульсів вхідного сигналу від заданого «нульового» моменту часу, або ділення частоти (збільшення періоду) вхідного сигналу. Лічильники характеризують модулем рахунку, який визначає максимальне число, до якого лічильник може вести підрахунок і на якому повертається в початковий стан, яким може бути будь-яке число менше модуля. Лічильники характеризуються способом кодування результатів рахунку – позиційні і непозиційні (наприклад код Грея); модулем рахунку – двійковий, десятковий, двійково-десятковий; з постійним або програмованим модулем; напрямом рахунку прямий (код лічби зростає і реверсивний (код рахунку зменшується); способом організації міжрозрядних зв’язків – з послідовним переносом (асинхронні лічильники), паралельним переносом (синхронні лічильники) і комбінованим переносом; типом тригерів, на яких побудований лічильник: Т-, JK-тригери, та динамічні D–тригери.

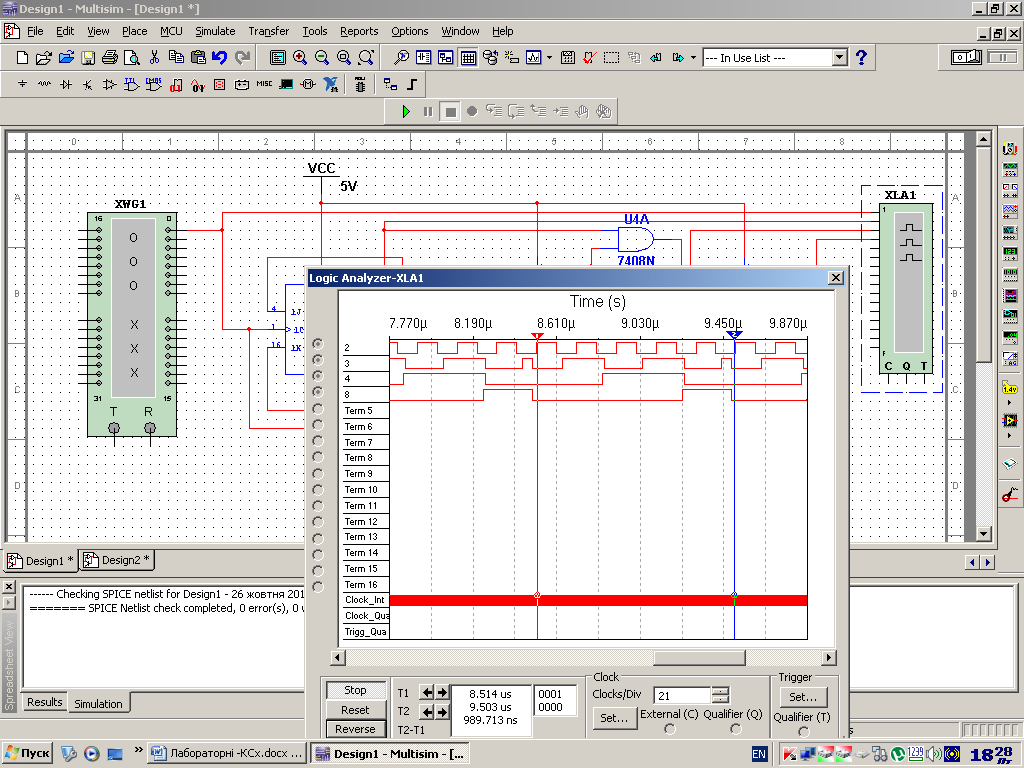

На рис.7.1 показана схема і часові діаграми роботи асинхронного двох розрядного лічильника на лічильних тригерах. Як видно із часових діаграм, модуль цього лічильника дорівнює 4, період сигналу Q0 дорівнює двом періодам сигналу С, а період сигналу Q1. дорівнює двом періодам сигналу Q0.

На рис.7.2 показана реалізація цього лічильника на D–тригерах з перемиканням тригерів по переходу синхросигналу С із 0 в 1 (по фронту синхросигналу), на рис. 7.3 те ж на JK-тригерах з перемиканням тригерів по переходу синхросигналу С із 1 в 0 (по спаду синхросигналу).

Рис. 7.1

| C |

| Q1 |

| Q0 |

Рис.7.2

| Q1 |

| Q0 |

| С |

Рис.7.3

Вказаний лічильник називається асинхронним тому, що зміна стану тригера Q1 відбувається при зміні стану тригера Q0, а не вхідного сигналу С. Чим більше асинхронний лічильник має розрядів, тим пізніше буде зміна стану його останнього розряду відносно вхідного сигналу і може приводити до неправильної роботи лічильника. На рис.7.4 показані часові діаграми роботи асинхронного лічильника рис.7.3 із яких видно наростаюче запізнення сигналів Q0 і Q1 відносно синхросигналу.

| С |

| Q1 |

| Q0 |

Рис.7.4

Цього недоліку не має синхронний лічильник, схема, якого побудована на JK-тригерах і показана на рис.7.5. Як видно із тут же приведених часових діаграм, сигнали Q0 і Q1 мають однакове запізнення відносно сигналу С.

| Q1 |

| Q0 |

| C |

| Q1 |

| Q0 |

Рис.7.5

Для побудови лічильників із більшою ніж 2 кількістю розрядів необхідно використовувати JK-тригери із більшою кількістю J і K входів, або вводити додаткові схеми дешифрування 1-их станів тригерів, як це показано на рис.7.6.

| С |

Рис.7.6

Лічильники можна використовувати як для прямого так і зворотного рахунку, для чого розрядні виходи лічильника повинні бути з прямих або інверсних виходів тригерів, відповідно. У всіх приведених лічильниках, модуль рахунку дорівнює 2n, де n-кількість розрядів лічильника. Для отримання довільного значення модуля рахунку, необхідно додатково ввести в схему лічильника дешифратор відповідного стану лічильника. Так, наприклад, схема лічильника рис.7.6 може бути перероблена під модуль рахунку 5 так, як це показано на рис.7.7. Для отримання модуля рахунку 5, необхідно розпізнати, коли лічильник встановиться в стан 101 (двійкове число 5) і по ньому виробити сигнал скидання лічильника в 0. Роботу цієї схеми лічильника демонструють часові діаграми рис.7.7: тут зверху вниз представлені часові діаграми синхросигналу від першого зліва розряду, до крайнього справа.

Рис.7.7

7.1.2. Регістри – це тригерні функціональні вузли комп’ютера, призначені для запису і тимчасового зберігання невеликої кількості двійкових слів комп’ютера (регістри центрального процесора, файлова пам’ять, кеш-пам’ять). Регістри являються найбільш швидкодіючою пам’яттю комп’ютера. По типу запису/виведення інформації регістри поділяються на паралельні (одночасне введення і виведення всіх розрядів слова, послідовні (порозрядне введення слова і паралельне і/або послідовне виведення) та універсальні, а по типу синхронізації – асинхронні або синхронні. Основою побудови регістрів є D–тригери і JK–тригери.

На рис. 7.8а-7.8в приведені декілька прикладів різних схем регістрів.

Рис.7.8а – паралельне введення і виведення

Рис.7.8б – послідовне введення/паралельне виведення

Рис.7.8в – паралельне введення/послідовне виведення

2018-01-21

2018-01-21 544

544