Арифметично-логічний пристрій (АЛП) – це функціональний вузол комп’ютера, призначений для виконання над двійковими числами арифметичних операцій додавання і віднімання та порозрядних логічних операцій інверсії, кон’юнкції та диз’юнкції. Управління операціями АЛП здійснюється зовнішніми командами. Функціонально АЛП складається із модуля логічних операцій, арифметичного модуля (суматора) і модуля дешифрування команд управління.

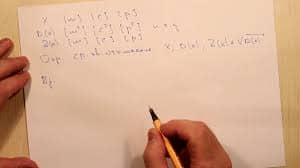

На рис.8.1 представлена структурна схема одно розрядного АЛП.

Рис.8.1.

Позначення на рисунку означають:

INVA - команда інверсії числа А,

A – перше вхідне число,

ENA – команда дозволу доступу числа А в АЛП,

B – друге вхідне число,

ENB - команда дозволу доступу числа В в АЛП,

Ci-вхідне перенесення від результату сумування в попередньому розряді,

Co – вихідне перенесення від результату сумування в даному розряді,

S – результат сумування в даному розряді.

F0 – 0-й розряд двох розрядної команди управління операціями АЛП,

F1 – 1-й розряд двох розрядної команди управління операціями АЛП.

Коди операцій F1F0 АЛП:

00- операція кон’юнкції (операція І),

01- операція диз’юнкції (операція АБО),

10 операція інверсії (операція НЕ),

11 операція арифметичного додавання.

Із однорозрядних АЛП рис. 8.1 будуються багато розрядні АЛП, як це показано на рис.8.2 (старший розряд зліва). Максимальне значення суми К-розрядного суматора АЛП дорівнює 2К-1. Це означає, що суматор АЛП обчислює суму двох чисел по модулю 2К. Якщо ця сума дорівнює або більше 2К, то виникає переповнення, і як наслідок, неправильне обчислення суми. Для запобігання неправильного результату в суматор АЛП вводять схему контролю переповнення, і якщо переповнення виявлено, то ця схема формує відповідне повідомлення і забороняє зберігати результат. В найпростішому випадку такою схемою є просто RS-тригер, який фіксує наявність перенесення старшого розряду суматора.

Рис.8.2

Схема багато розрядного АЛП рис.8.2 називається схемою з послідовним переносом. Її недоліком є те, що результат сумування появляється із затримкою, яка дорівнює сумі затримок всіх розрядів АЛП. Зменшення затримки результату сумування можна досягти за рахунок ускладнення схеми. Так, наприклад, для зменшення затримки результату сумування в два рази можна поступити наступним чином: К-розрядний суматор розбивається на дві групи з однаковою кількістю розрядів: молодша група включає розряди від 20 до 2К/2-1, а старша від 2К/2 до 2К-1. Перенесення між молодшою і старшою групами розривається, обчислення часткових сум в групах проводиться самостійно, причому в старшій групі обчислення проводяться паралельно для двох випадків, коли перенесення між групами немає і коли перенесення між групами є. Результат сумування визначається аналізом перенесення із молодшої групи: якщо тут перенесення не було, то із старшої групи береться результат, обчислений без врахування перенесення із молодшої групи, а якщо було – то результат обчислений із врахуванням наявності перенесення із молодшої групи. Аналогічно приведений алгоритм, можна застосувати для розбиття К-розрядного суматора на 4, 8,.., груп аж до отримання в групі всього двох членів і зведення затримки до величини затримки в одному розряді. Проте, платою за зменшення затримки в суматорі є значне ускладнення алгоритму його роботи.

Схема однорозрядного арифметичного модуля АЛП (повного суматора) показана на рис.8.3.

Рис.8.3.

Схема модуля логічних операцій показана на рис.8.4.

Рис.8.4.

Схема модуля декодера операцій показана на рис.8.5.

Рис.8.5.

Основні операції АЛП:

| F1 | F0 | ENA | ENB | INVA | INC | Операція |

| А | ||||||

| В | ||||||

| ||||||

| ||||||

| А+В | ||||||

| А+В+1 | ||||||

| А+1 | ||||||

| В+1 | ||||||

| В-А | ||||||

| В-1 | ||||||

| -А | ||||||

А

| ||||||

А

| ||||||

| -1 |

2018-01-21

2018-01-21 523

523