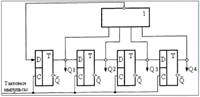

В отличие от дешифраторов распределители последовательно активизируют свои выходы при каждом тактовом импульсе. Логическая схема распределителя представлена на Рис. 57. Основу распределителя составляет регистр последовательного сдвига, «Q» выходы которого подключены на вход элемента «ИЛИ-НЕ».

Рис. 57. Структура распределителя.

Принцип работы распределителя состоит в следующем. Первоначально все выходы «Q» регистра последовательного сдвига обнулены, поэтому обнулены все входы логического элемента «ИЛИ-HE», выходной сигнал которого подается на вход «D» триггера младшего разряда этого регистра. В результате этого при полном обнулении регистра на входе «D» триггера младшего разряда появляется единичный сигнал. После первого тактового импульса триггер младшего разряда переходит в единичное состояние и его сигнал «Q1» сразу же перекидывает элемент «ИЛИ-HE» в нулевое состояние, которое будет сохраняться до тех пор, пока регистр сдвига не обнулится снова. Последующие тактовые импульсы будут смещать единичный выход в строну старших разрядов регистра, в то время как на их место будут становиться нулевые символы (сигналы). Как только единица сместится за область старшего разряда все триггеры регистра сдвига вновь окажутся «нулевыми», а на входе «D» триггера младшего разряда регистра сдвига опять появится единица, которая снова будет последовательно смещаться по разрядам регистра при каждом следующем тактовом импульсе.

48. Структура сумматора. Принцип его работы

В цифровых системах автоматики сумматоры применяют для выполнения любых арифметических действий над двоичными числами (цифровыми сигналами). Использование правил арифметического сложения целых чисел в сочетании с операциями логических сдвигов (вправо или влево) позволяет вычислительным устройствам систем цифровой автоматики выполнять любые алгебраические операции над двоичными числами (сигналами). Поэтому сумматоры являются частью АЛУ (алгебраическо- логических устройств) этих систем. Сумматоры работают по арифметическим правилам, изложенным в таблице 9.

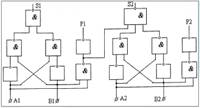

По этим правилам происходит поразрядное сложение двух двоичных чисел с учетом значения единицы переноса в младшем (предыдущем) разряде. Логическая схема двухразрядного сумматора представлена на Рис. 58.

Рис. 58. Структура двухразрядного сумматора.

Принцип работы каждого разряда сумматора определен параметрами отдельной строки таблицы 9. Так если в младшем разряде обеих слагаемых находятся нули (т.е. А1=В1=0), то появление нулей на элементах «И-НЕ» второго уровня обеспечивает на их выходах появление единиц, которые элементом «И-НЕ» третьего уровня обнуляют результат суммы в этом разряде т.е. S1=0. Аналогично если А1=В1=0 то элемент «И-НЕ» первого уровня на выходе дает единицу, которая инвертором превращает в ноль единицу переноса, т.е. и в этом случае Р1=0. Появление единицы в суммируемом разряде одного из слагаемых (А 1=1 или В 1=1) вызывает обнуление входов только одного из элементом «И-НЕ» второго уровня, поэтому один из этих элементов всегда дает нулевой выход, что вызывает на выходе элемента «И-НЕ» третьего уровня появление единицы (т.е. в этом случае Sl=l).

Появление единицы с суммируемом разряде только у одного из слагаемых не меняет единичного выхода элемента «И-НЕ» первого уровня, поэтому в этом случае единица переноса остается на нулевом уровне. Только в случае двух единиц в слагаемом разряде единица переноса по той же причине может быть на единичном уровне, но сумма слагаемых разрядов в этом случае нулевая.

2018-02-14

2018-02-14 438

438