Защита памяти основана на использовании сегментации. Сегмент — это блок адресного пространства памяти определенного назначения. К элементам сегмента возможно обращение с помощью различных инструкций процессора, использующих разные режимы адресации для формирования адреса в пределах сегмента. Максимальный размер сегмента для процессоров 8086 и80286 составлял 64 Кб, в 32-разрядных процессорах этот предел отодвигается до 4 Гб. Сегменты памяти выделяются задачам операционной системой, но в реальном режиме любая задача может переопределить значение сегментных регистров, задающих положение сегмента в пространстве памяти, и “залезть” в чужую область данных или кода. В защищенном режиме сегменты тоже распределяются операционной системой, но прикладная программа сможет использовать только разрешенные для нее сегменты памяти, выбирая их с помощью селекторов из предварительно сформированных таблиц дескрипторов сегментов. Селекторы представляют собой 16-битные указатели, загружаемые в сегментные регистры процессора.

Дескрипторы — это структуры данных, используемые для определения свойств программных элементов (сегментов, вентилей и таблиц). Дескриптор определяет положение элемента в памяти, размер занимаемой им области (лимит), его назначение и характеристики защиты. Защита памяти с помощью сегментации не позволяет:

• использовать сегменты не по назначению (например, пытаться трактовать область данных как коды инструкций);

• нарушать права доступа (пытаться модифицировать сегмент, предназначенный только для чтения, обращаться к сегменту, не имея достаточных привилегий, и т. п.);

• адресоваться к элементам, выходящим за лимит сегмента;

• изменять содержимое таблиц дескрипторов (то есть параметров сегментов), не имея достаточных привилегий.

Страничное управление памятью

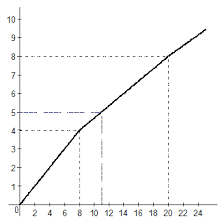

Страничное управление (Paging) является дополнительным средством для организации виртуальной памяти. В отличие от сегментации, которая организует программы и данные в модули различного размера, страничная организация подразделяет модули на множество небольших страниц одинакового размера. Страницы не имеют прямой связи с логической структурой данных или программ. В то время как селекторы можно рассматривать как логические имена модулей кодов и данных, страницы представляют части этих модулей. Учитывая обычное свойство локальности (близкого расположения требуемых ячеек памяти) кода и ссылок на данные, в оперативной памяти в каждый момент времени следует хранить только небольшие области сегментов, необходимые активным задачам. Эту возможность (а следовательно, и увеличение допустимого числа одновременно выполняемых задач при ограниченном объеме оперативной памяти) и обеспечивает страничное управление памятью.

Механизм страничного управления использует двухуровневую табличную трансляцию линейного адреса в физический.

Переключение задач

Защищенный режим предоставляет средства переключения задач. Состояние каждой задачи (значение всех связанных с ней регистров процессора) может быть сохранено в специальном сегменте состояния задачи (TSS), на который указывает селектор в регистре задачи. При переключении задач достаточно загрузить новый селектор в регистр задачи, и состояние предыдущей задачи автоматически сохранится в ее TSS, а в процессор загрузится состояние новой (возможно, и ранее прерванной) задачи и начнется (продолжится) ее выполнение.

Обмен данными по прерыванию

Аппаратные прерывания вызываются внешними устройствами и теми компонентами компьютера, которые требуют немедленной обработки своей информации и приходят асинхронно по отношению к исполняемой программе. Прерывание можно рассматривать как некоторое особое событие в системе, которое заставляет процессор приостановить выполнение своей программы для реализации некоторой затребованной деятельности. Программные обработчики аппаратных прерываний инициализируют блочный обмен или выполняют одиночную операцию пересылки по системной шине с внешним устройством. Практически это основной способ инициализации обмена. Прерывания существенно увеличивают эффективность вычислительной системы, поскольку они позволяют внешним устройствам "обращать на себя внимание" процессора только по мере надобности.

Прерывания и исключения (разновидности и характеристики)

Нарушают нормальный ход выполнения программы, для обработки внешних событий или сообщения р возникновении особых условие или ошибок.

Прерывания:

Аппаратные (маскируемые INTR/немаскируемые NMI)

Программные

Маскируемые - вызываются аппаратно сигналом на входе процессора INTR (при установленном флаге разрешения прерывания). Затем флаг сбрасывается и запускается обработка прерывания.

Немаскируемые – вызывают сброс регистров процессора и перезагрузку системы.

Исключения:

Отказ (fault) – обнаруживается и обслуживается ДО выполнения инструкции, вызвавшей ошибку. Управление возвращается на ту же команду

Ловушка (trap) - обнаруживается и обслуживается ПОСЛЕ выполнения инструкции, вызвавшей ошибки. Управление возвращается на следующую команду

Аварийное завершение (abort) – не позволяет точно установить инструкцию, его вызвавшую. (сообщения о серьезных ошибках)

Особенности архитектуры CISС процессоров

Complex instruction set computer — вычисления со сложным набором команд. Процессорная архитектура, основанная на усложнённом наборе команд. Типичными представителями CISC являются микропроцессоры семейства x86 (хотя уже много лет эти процессоры являются CISC только по внешней системе команд: в начале процесса исполнения сложные команды разбиваются на более простые микрооперации (МОП’ы), исполняемые RISC-ядром).

2018-02-14

2018-02-14 471

471