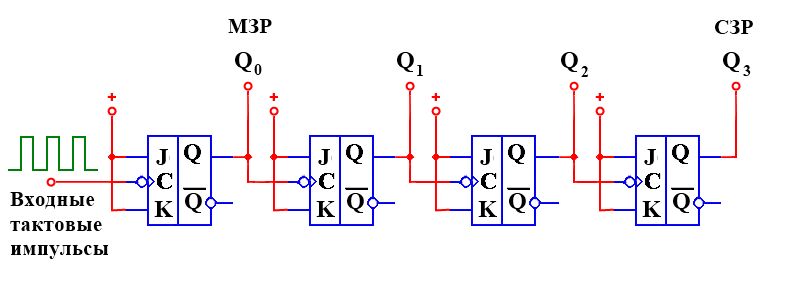

С помощью последовательного соединения JK-триггеров (выход Q каждого триггера подключен к тактирующему входу следующего) легко получить «делитель 2n», или двоичный счетчик. Заметим, что непосредственное действие выхода Q каждого триггера на тактовый вход последующего происходит только по спаду (заднему фронту) сигнала на тактовом входе.

Делитель 2n -

При каскадном включении четырех JK-триггеров мы получаем счетчик-делитель на 16, то есть на выходе последнего триггера формируются прямоугольные импульсы, следующие с частотой, равной 1/16 частоты входного тактового сигнала. На каждом каскаде (триггере) происходит деление частоты на 2, итого делитель для 4 каскадов будет 2 в степени 4 (2х2х2х2 = 16).

Счетчик -

Каждый тактовый импульс ведет к изменению состояния выходных сигналов Q, при этом эти изменения соответствуют правилам двоичного счета, где выход первого триггера соответствует младшему значащему разряду (на графике МРЗ), а последний выход (четвертого триггера) – старшему значащему разряду (на графике СЗР). Рассматривая временную диаграмму для всех четырех выходов Q мы видим увеличение значения с каждым тактом от 0 до 15 (в двоичном представлении). Подавая содержимое выходов на индикаторы (например, светодиодные) можно строить схемы позволяющие представлять данные подсчета в понятной форме для человека.

Этот счетчик имеет очень широкое применение в промышленности, поэтому выпускаются различные модификации в виде однокристальных микросхем, для различных форматов счета, такие как 4-разрядные, двоично-десятичные и много цифровые счетчики.

2020-08-05

2020-08-05 364

364