Для правильної роботи арифметико-логічного пристрою комп’ютера на виконання операції додавання чи віднімання в доповняльному коді нам потрібно синтезувати такі основні функціоналні вузли комп’ютера: лінійний дешифратор на три входи х1-х3 і вісім прямих виводів F 0 – F 7; схема контролю за парністю; схема перетворювача прямого коду в доповняльний.

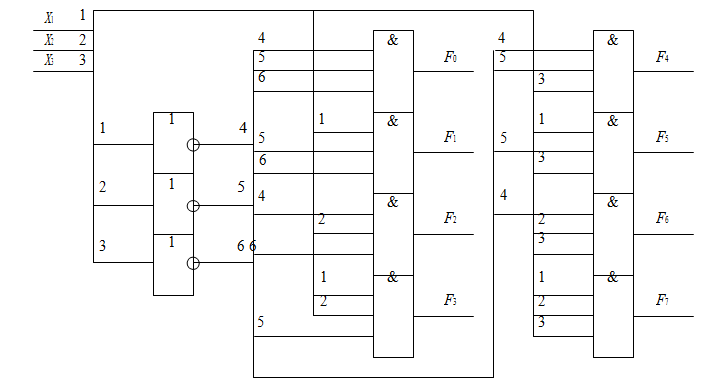

Проектування лінійного дешифратора на три входи х1-х3 і вісім прямих виводів F 0 – F 7.

Логіка функціонування дешифратора задається таблицею іс-тинності (табл. 1.1.).

Таблиця 1. – Таблиця істинності лінійного дешифратора «3→8»

| Х 3 | Х 2 | Х 1 | F 0 | F 1 | F 2 | F 3 | F 4 | F 5 | F 6 | F 7 |

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

Рис. 3. Принципіальна схема лінійного дешифратора «3→8» з прямими виходами

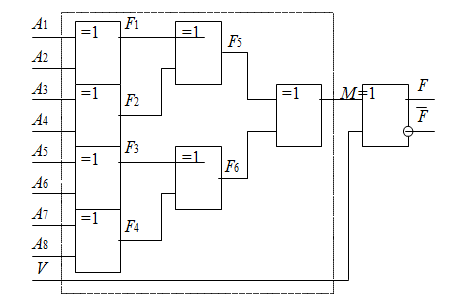

У комп'ютерах широко використовується контроль парності (синонім – за паритетом або відповідністю). Цей спосіб заснований на допущенні, що в двійковому числі найчастіше виникають одиничні помилки – втрата або поява зайвої одиниці. У обох випадках число одиниць зміниться на одну. Якщо двійкове число мало непарне число одиниць, то після одиничної помилки воно виявиться парним і навпаки.

На практиці контроль парності здійснюється таким чином. Для підвищення ефективності контролю двійкове слово розбивається на частини, як правило, байти. До кожного байта додається додатковий контрольний розряд. Вміст контрольного розряду залежить від вибраного способу контролю (за парністю або непарністю). При контролі за парністю значення контрольного розряду виби рається таким, щоб загальне число одиниць у байті й контрольному біті було парним.

У разі контролю за парністю значення контрольного (паритетного) біта визначається додаванням за модулем два значень розрядів байта:

Fк.п = A1 ⊕ A2 ⊕ A3 ⊕ A4 ⊕ A5 ⊕ A6 ⊕ A7 ⊕ A8.

У разі контролю за непарністю значення контрольного біта набуває такого виразу:

Fк.н = A1 ⊕ A2 ⊕ A3 ⊕ A4 ⊕ A5 ⊕ A6 ⊕ A7 ⊕ A8 = Fк.п.

Умову парності отримуємо складанням за модулем два восьмирозрядного слова, що реалізується за допомогою ступінчастого включення двовходових елементів ВИКЛЮЧАЛЬНЕ ЧИ (рис. 1.5):

• на першому рівні отримують функції F1 – F4:

F1 = А1⊕A2;

F2 = А3⊕А4;

F3 = A5⊕A6;

F4 = А7⊕A8;

• на другому і третьому рівнях реалізуються функції:

F5= F1⊕F2;

F6 = F3⊕F4;

М = F5⊕F6.

Для задання ознаки контролю вводиться керуючий сигнал V, який разом із сигналом М поступає на входи схеми виключальне ЧИ в четвертому рівні; на прямому й інверсному виходах цього рівня формуються пряме й інверсне значення контрольного розряду:

F = M ⊕V;

F = M ⊕V.

Рис. 4. Схема контролю за парністю

Проектування схеми перетворювача прямого коду в доповняльний.

Доповняльний код додатного двійкового числа збігається з його прямим і оберненим кодами. Доповняльний код від’ємного двійкового числа утворюється з його оберненого коду додаванням до молодшого розряду одиниці.

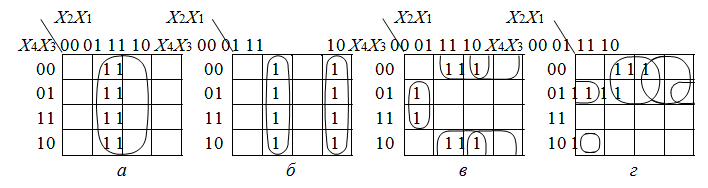

Рис. 5. Карта Карно для функцій перетворювача прямого коду в доповняльний: а – Y1; б – Y2; в – Y3; г – Y4

На основі карт Карно з урахуванням знакового розряду Хзн прямого коду для функцій Y1, Y2, Y3, Y4, що представляють виходи перетворювача, отримуємо:

Y зн = X зн; Y 1 = X 1; Y 2 = X 2⊕ X 1 X зн;

Y 3 = X 3⊕(X 2˅ X 1) X зн; Y 4 = X 4⊕ (X 3˅ X 2˅ X 1) X зн.

У загальному вигляді для Yi справедливе рівняння:

Yi = X i ⊕(X i −1 ⊕∨ X i −2 ˅…˅ X 1) X зн.

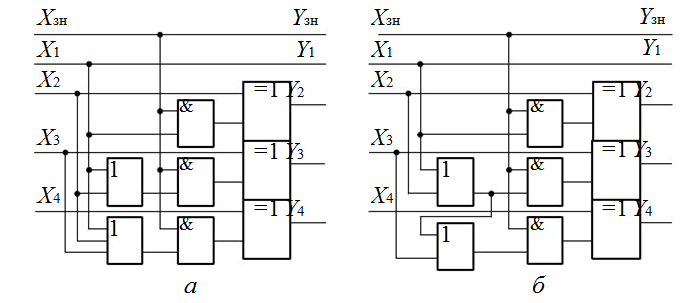

Схеми перетворювачів прямого коду в доповняльний на основі виразів показано на рис. 6

Рис. 6. Схеми перетворювачів прямого коду в доповняльний

Рис. 6. Схеми перетворювачів прямого коду в доповняльний

2020-09-24

2020-09-24 125

125