Лекция №16 Методика программирования контроллера ПДП.

Выполняется процессором в программном режиме и включает следующие действия:

1. Инициализация – должна выполняться по всем каналам, даже если они не используются. В машинах семейства IBM PC выполняется BIOS.

- DREQ – высокий уровень сигнала;

- DACK – низкий уровень сигнала;

- Цикл записи – нормальный;

- Приоритеты – фиксированные;

- Режим управления ПДП – ВУ-память;

- Все каналы маскированы.

2. Программирование канала КПДП.

1. Запрет работы канала на время программирования.

Операция индивидуального маскирования выбранного канала:

Запись по адресу Ah следующей информации:

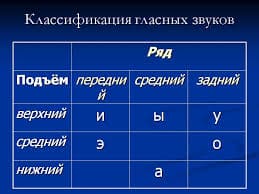

| Маска | Канал |

2. Установка режима работы канала.

Запись по адресу Bh позволяет установить параметры режима работы.

3. Сброс триггера “Первый/последний”.

Запись произвольного значения по адресу Ch.

4. Запись младших бит адреса в регистр адреса базовый, регистр адреса текущий.

5. Запись старших бит адреса: A 16- A 23 в регистр страниц.

6. Запись числа, которое на 1 меньше, чем количество байт, которые необходимо передать по каналу ПДП.

7. Разрешение работы канала.

Нужно сбросить маску в 0.

Пример реализации методики программирования.

Канал 1 (КАМАК), запись в ОЗУ одиночными символами 1000 байт.

Var

Buf: array [1..500] of word;

addr _ buf: longint;

Apage, Aofs: word;

Begin

{1} Port [$ A ]:=5;

{2} Port [$ B ]:=$45;

Seg (Buf); {Возвращает сегментную часть аргумента}

ofs (Buf); {Смещение}

addr _ buf:= seg (Buf);

addr _ buf:=(addr _ buf shl 4) + ofs (Buf); {узнали физический адрес}

Apage:= addr _ buf shr 16;

Aofs:= addr _ buf and $ FFFF;

Port [$ C ]:=0; {Сброс триггера первый/последний}

Port [2]:= Lo (Aofs); {Триггер первый/последний = 1}

Port [2]:= Hi (Aofs); {Триггер первый/последний = 0}

Port [$83]:= Apage;

Port [3]:= Lo (sizeof (Buf)-1)); {999}

Port [3]:= Hi (Sizeof (Buf)-1);

Port [$ A ]:=1; {Разрешение работы канала}

End.

Если интерфейс установит DREQ =1, то КПДП будет выполнять обмен данными так, как его запланировали.

В качестве интерфейса ВУ используется интерфейс КАМАК. Контроллер крейта КАМАК для обмена в режиме ПДП содержит 2 дополнительных регистра.

Адрес 24 Fh - Регистр управления ПДП, адрес 24 Fh – регистр состояния ПДП.

Рис. 17.1 Регистр управления ПДП контроллера ККП3.

Регистр управления обменом ПДП доступен процессору для записи, определяет: число байтов в словах, передаваемых между модулями КАМАК и ОЗУ ЭВМ – биты 1,0; режим окончания обмена – бит 2; направление передачи данных в режиме ПДП – бит 3; номер активного контроллера КАМАК – биты 4,5; разрешение/запрет формирования сигнала DREQ 1 –бит 6. Бит 6 аппаратно сбрасывается по окончании передачи сигналом EOP.

| 1/0 |

Рис. 17.2 Формат регистра состояния ПДП контроллера ККП3.

Регистр состояния операции ПДП доступен процессору для чтения. Бит 7 регистра показывает состояние операции ПДП: 0/1 – ПДП операция выполняется / закончена. Бит устанавливается сигналом на линии EOP.

17.1 Алгоритм выполнения КК операции ПДП.

D 3, D 6 – РУ ПДП КК.

Чтение данных из ФМ в ОЗУ: ФМ→КК→ОЗУ.

При чтении данных из модуля в ОЗУ выполняются следующие действия:

1. Запуск цикла КАМАК.

2. Устанавливает сигнал DREQ – запрос ПДП.

3. Передача по каналу ПДП.

4. Снимает сигнал DREQ.

Запись данных из ОЗУ в модуль КАМАК: ОЗУ→КК→ФМ.

При записи данных из ОЗУ в ФМ выполняются следующие действия:

1. Установка сигнала DREQ в КПДП.

2. Передача по каналу ПДП 1-го, 2 или 3 байта.

3. Сброс сигнала DREQ.

4. Запуск цикла КАМАК.

Если указано условие прекращение обмена по Q =0, то контроллер в каждом цикле будет проверять Q.

2014-02-02

2014-02-02 399

399