Более подробно рассмотрим схему таймеров/счетчиков МК ATmega 128 на примере 16-разрядного таймера/счетчика 1. Он имеет идентичную структуру с таймером/счетчиком 3.

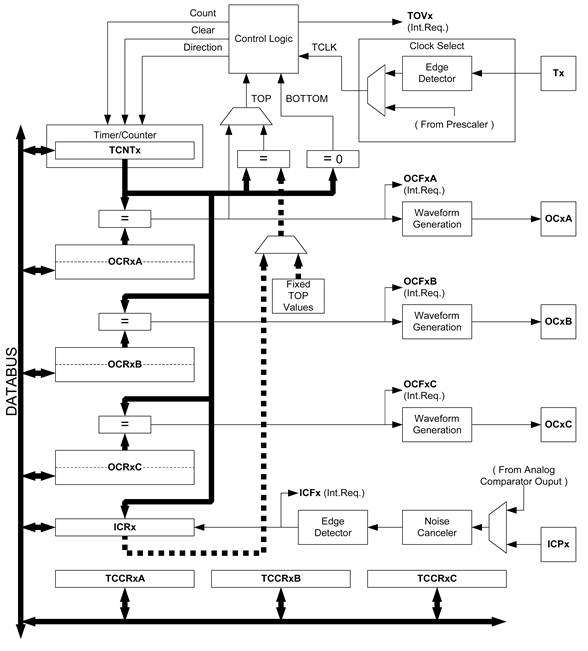

Блок-схема таймера/счетчика 1 приведена на рис. 5.3. Буквой «x» обозначен номер рассматриваемого таймера/счетчика (x=1).

Рис. 5.3. Блок-схема таймера/счетчика 1, 3 МК ATmega 128.

Таймер/счетчик 1 содержит базовый счетчик TCNT1H:TCNT1L (Timer/Counter 1), имеющий шестнадцать разрядов. При поступлении тактирующего сигнала на вход схемы счетчика значение базового счетчика, в зависимости от выбранного режима работы, инкрементируется или декрементируется. Кроме того, в состав таймера-счетчика входят регистры управления TCCR1A, TCCR1B, TCCR1C (Timer/Counter 1 Control Register), два разряда регистра запросов, прерывания TIFR и столько же разрядов регистра маскирования прерываний TIMSK. Регистры TIFR и TIMSK являются общими для всех таймеров-счетчиков микроконтроллера.

Разряд регистра TIFR (Timer/Counter Interrupt Flag Register) устанавливается в единичное состояние при формировании в таймере-счетчике определенного запроса прерывания. В регистре масок прерываний TIMSK (Timer/Counter Interrupt Mask Register) устанавливаются разрешения/запрещения прерываний таймера/счетчика 1. Разряд регистра TIFR сбрасывается в нулевое состояние аппаратно при переходе микроконтроллера к выполнению соответствующей прерывающей программы или программно при выполнении команды установки бита в единичное состояние.

В состав таймера/счетчика, выполняющего функцию сравнения или ШИМ, входят регистры сравнения OCR1АH:OCR1АL, OCR1BH:OCR1BL, OCR1CH:OCR1CL (Output Compare Register), а в состав таймера/счетчика, выполняющего функцию захвата, — регистр захвата ICR1H:ICR1L (Input Capture Register). Разрядность регистров OCR1 и ICR1 равна разрядности базового счетчика TCNT1.

16-разрядный таймер/счетчик 1 может получать тактовый сигнал от СLК, СLК после предварительного делителя и от внешнего вывода. Кроме того, его можно остановить. При внешнем тактировании таймера/счетчика 1 внешний сигнал синхронизируется частотой тактового генератора CPU.

Наилучшие точность и разрешение 16-разрядный таймер/счетчик 1 обеспечивает при наименьшем коэффициенте предварительного деления. С другой стороны, высокий коэффициент предварительного деления удобен при реализации таймером/счетчиком 1 низкоскоростных функций или точной синхронизации редко происходящих действий. Таймер/счетчик1 поддерживает функции сравнения выхода, используя регистры сравнения выходов А, В и C - OCR1А, OCR1В, OCR1C в качестве источников данных, сравниваемых с содержимым таймера/счетчика 1.

Таймер/счетчик 1 может быть использован в качестве 8, 9 или 10-разрядного широтно-импульсного модулятора. В этом режиме счетчик и регистры OCR1A/OCR1B/OCR1С работают как сдвоенный самостоятельный ШИМ со сцентрированными импульсами, без формирования ложных импульсов.

Функция захвата входа таймера/счетчика 1 обеспечивает захват содержимого таймера/счетчика 1 в регистр захвата входа, запускаемый внешним событием на выводе входа захвата IC1. Реальные установки захвата события определяются регистром управления таймером/счетчиком 1 TCCR1B. Кроме того, для переключения входа захвата может быть использован аналоговый компаратор. Если разрешена функция подавления шума, действительные условия переключения события захвата тестируются четырьмя выборками, прежде чем захват будет активирован. Тестирование сигнала на входном выводе производится с частотой тактирования ядра МК.

Базовый счетчик (Counter Unit)

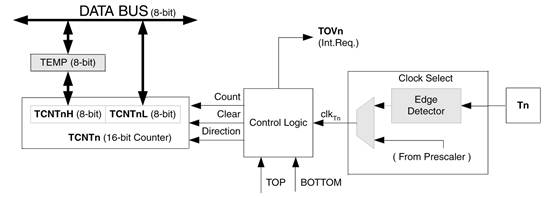

Основной частью 16-разрядного таймера/счетчика 1 является реверсивный базовый счетчик TCNTn. Его блок-схема изображена на следующем рисунке 5.4:

Рис. 5.4. Блок-схема базового счетчика.

Расшифруем сигналы изображенные на блок-схеме.

Count – инкремент или декремент величины базового счетчика TCNTn.

Direction – Выбор направления счета.

Clear – очистка базового счетчика TCNTn.

clkTn – тактирующий сигнал таймера/счетчика 1.

TOP – Сигнализирует, что счетчик достиг максимального значения.

BOTTOM – Сигнализирует, что счетчик достиг нулевого значения.

16-разрядный счетчик состоит из двух 8-разрядных регистров TCNT1H:TCNT1L, причем обращение к старшему регистру происходит косвенно, через временный регистр TEMP. Это сделано для того, чтобы CPU могло считывать/записывать и старший и младший байты этого регистра одновременно. Если основная программа и подпрограммы обработки прерываний используют обращение к регистрам посредством TEMP, то прерывания должны быть запрещены на время обращения из основной программы. Более подробно этот вопрос описан в разделе «Обращение к 16-разрядным регистрам».Отметим, что запись в регистр TCNT во время работы счетчика может дать непредсказуемые результаты.

В зависимости от режима работы значение базового счетчика может быть очищено, увеличено, или уменьшено на каждом цикле тактирования.

На рисунке 5.4 представлена блок-схема базового счетчика. Элементы, которые непосредственно не являются частью базового счетчика, обозначены серым цветом.

Как уже отмечалось, таймер/счетчик 1 может получать тактовый сигнал от СК, СК после предварительного делителя и от внешнего вывода. Способ тактирования определяется битами CSn2:0 (Clock Select). Если биты CSn2:0 равны нулю – счетчик остановлен. Однако значение TCNT может быть изменено ЦП в независимости от тактирующего сигнала счетчика clkTn.

Режим работы таймера/счетчика определяется установкой битов режима генерации сигнала (Waveform Generation mode) WGMn3:0. Они расположены в регистрах управления таймера/счетчика А и В (TCCRnA и TCCRnB)

Флаг переполнения таймера/счетчика TOVn (Timer/Counter Overflow) устанавливается в соответствии с режимом работы и используется для генерации прерывания по переполнению базового счетчика.

2014-02-02

2014-02-02 1397

1397