Содержание

Содержание. 1

1 Микроконтроллер AT90S8535 фирмы Atmel 5

2 Описание выводов. 6

3 Кварцевый генератор. 7

4 Обзор архитектуры AT90S8535. 8

4.1 Файл регистров общего назначения. 11

4.2 Арифметико-логическое устройство - АЛУ.. 12

4.3 Загружаемая память программ. 12

4.4 EEPROM память данных. 12

4.5 Статическое ОЗУ данных. 13

4.6 Время выполнения команд. 14

4.7 Пространство ввода/вывода. 14

4.8 Status Register (SREG) 15

4.9 Stack Pointer (SP) 17

4.10 Сброс и обработка прерываний. 18

4.10.1 Источники сброса. 19

4.10.1.1 Сброс по выключению питания. 20

4.10.1.2 Внешний сброс. 20

4.10.1.3 Сброс от сторожевого таймера. 21

4.10.2 Обработка прерываний. 21

4.10.2.1 General Interrupt Mask Register (GIMSK) 21

4.10.2.2 General Interrupt Flag Register (GIFR) 22

4.10.2.3 Timer/Counter Interrupt Mask Register (TIMSK) 23

4.10.2.4 Timer/Counter Interrupt Flag Register (TIFR) 25

4.10.3 Внешние прерывания. 27

4.10.4 Время реакции на прерывание. 27

4.10.5 MicroController Unit Control Register (MCUCR) 28

4.11 Режимы пониженного энергопотребления. 30

4.11.1 Idle mode. 30

4.11.2 Power-Down. 31

4.11.3 Power-Save. 32

5 Таймеры/счетчики. 32

5.1 8-разрядный таймер/счетчик 0. 33

5.1.1 Timer/Counter0 Control Register (TCCR0) 34

5.1.2 Timer/Counter0 (TCNT0) 35

5.2 16- разрядный таймер/счетчик 1. 36

5.2.1 Timer/Counter1 Control Register A (TCCR1A) 38

5.2.2 Timer/Counter1 Control Register B (TCCR1B) 39

5.2.3 Timer/Counter1 (TCNT1H, TCNT1L) 41

5.2.4 T/C1 Output Compare Register (OCR1AH, OCR1AL) 42

5.2.5 T/C1 Output Compare Register (OCR1BH, OCR1BL) 42

5.2.6 Timer/Counter1 Input Capture Register (ICR1H, ICR1L) 43

5.2.7 Таймер/счетчик 1 в режимеШИМ.. 44

5.3 8- разрядный таймер/счетчик 2. 47

5.3.1 Timer/Counter2 Control Register (TCCR2) 48

5.3.2 Управление тактовым сигналом. 48

5.3.3 Режим таймера. 49

5.3.4 Режим ШИМ.. 51

5.3.5 Асинхронный режим работы.. 52

5.3.6 Asyncronous Status Register (ASSR) 53

6 Сторожевой таймер. 56

6.1 Назначение cторожевого таймера. 56

6.2 Watchdog Timer Control Register (WDTCR) 58

7 Чтение и запись в энергонезависимую память. 59

7.1 EEPROM Address Register (EEARH, EEARL) 60

7.2 EEPROM Data Register (EEDR) 60

7.3 EEPROM Control Register (EECR) 61

7.4. Меры предосторожности при работе с EEPROM.. 63

8 Последовательный периферийный интерфейс SPI 64

8.1. Общие сведения. 64

8.2. Функционирование модуля SPI 65

8.2.1 SPI Control Register (SPCR) 67

8.2.2 SPI Status Register (SPSR) 68

8.2.2 SPI Data Register (SPDR) 69

8.3. Режимы передачи данных. 70

8.4. Использование вывода SS. 71

9 Универсальный асинхронный приемопередатчик UART. 73

9.1 Передача данных. 73

9.2 Прием данных. 75

9.3 Управление UART. 78

9.3.1 UART I/O Data Register (UDR) 78

9.3.2 UART Status Register (USR) 78

9.3.3 UART Control Register (UCR) 80

9.3.4 Baud Rate Generator 81

9.3.5 UART Baud Rate Register (UBRR) 83

10 Аналоговый компаратор. 83

10.1. Функционирование компаратора. 83

10.2 Analog Comparator Control and Status Register (ACSR) 84

11 Аналого-цифровой преобразователь. 87

11.1. Общие сведения. 87

11.2 Функционирование модуля АЦП.. 87

11.3 ADC Control and Status Register (ADCSR) 88

11.4 ADC Data Register (ADCL, ADCH) 94

11.5 ADC Multiplexer Select Register (ADMUX) 94

11.6 Повышение точности преобразования. 95

11.7 Параметры АЦП.. 97

12 Порты ввода/вывода. 97

12.1 Общие сведения. 97

12.2 Обращение к портам ввода/вывода. 98

12.3. Конфигурирование портов ввода/вывода. 100

13 Программирование памяти. 102

13.1 Биты блокировки памяти (Lock Bits) 102

13.2 Биты конфигурации (Fuse bits) 102

13.3 Код устройства. 103

14 Электрические характеристики. 103

14.1 Максимально допустимые параметры.. 103

14.2 Характеристики по постоянному току. 105

14.3 Параметры внешнего тактового сигнала. 106

15 Информация для заказа. 106

16 Список регистров AT90S8535. 108

1 Микроконтроллер AT90S8535 фирмы Atmel

AT90S8535 - экономичный 8 битовый КМОП микроконтроллер, построенный с использованием расширенной RISC архитектуры AVR. Исполняя по одной команде за период тактовой частоты, AT90S8535 имеет производительность около 1MIPS на МГц (1 миллион операций в секунду), что позволяет разработчикам создавать системы оптимальные по скорости и потребляемой мощности.

В основе ядра AVR лежит расширенная RISC архитектура, объединяющая развитый набор команд и 32 регистра общего назначения. Все 32 регистра непосредственно подключены к арифметико-логическому устройству (АЛУ), что дает доступ к любым двум регистрам за один машинный цикл. Подобная архитектура обеспечивает десятикратный выигрыш в эффективности кода по сравнению с традиционными CISC микроконтроллерами.

AT90S8535 имеет следующие особенности:

- 8кБ загружаемой FLASH-памяти;

- 512 байт EEPROM;

- 512 байт SRAM;

- 32 линии ввода/вывода общего назначения;

- 32 рабочих регистра;

- настраиваемые таймеры/счетчики с режимом совпадения;

- внешние и внутренние прерывания;

- программируемый универсальный последовательный порт UART;

- программируемый сторожевой таймер со встроенным генератором;

- SPI - последовательный порт для загрузки программ;

- три выбираемых программно режима пониженного энергопотребления.

Микросхемы производятся с использованием технологии энергонезависимой памяти высокой плотности фирмы Atmel. Загружаемая FLASH-память на кристалле может быть перепрограммирована прямо в системе через последовательный интерфейс SPI или доступным программатором энергонезависимой памяти.

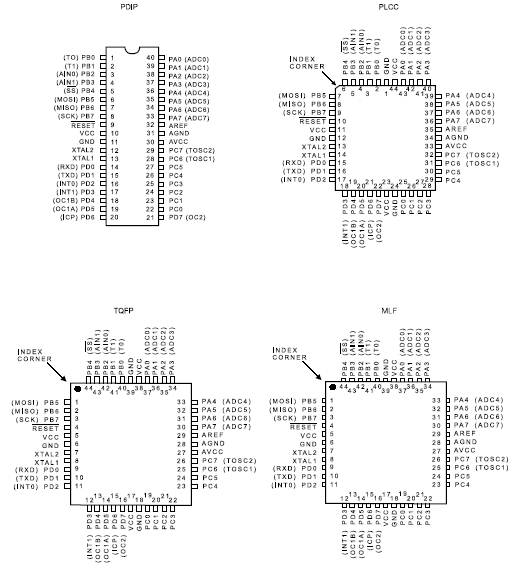

Микросхема AT90S8535 выпускается в четырех типах корпусов: PDIP, PLCC, TQFP и MLF (рис.2.1). Основное назначение выводов следующее:

VCC - вывод источника питания

GND – цифровая земля

AVCC – вывод для подключения питания аналоговых цепей

AREF – вывод для подключения опорного напряжения

AGND – аналоговая земля

PORTA, PORTB, PORTC, PORTD, (PA7..PA0, PB7..PB0, PC7..PC0, PD7..PD0) - Порты A, B, C и D являются 8-битовыми двунаправленными портами ввода/вывода. Некоторые выводы портов снабжены альтернативными функциями (указанны в скобках), которые будут описаны ниже. Выходные буферы портов могут поглощать ток до 20мА и непосредственно управлять светодиодными индикаторами.

RESET - Вход сброса. При удержании на входе низкого уровня в течение двух машинных циклов (если генератор работает), происходит аппаратный сброс.

XTAL1 - Вход инвертирующего усилителя генератора и вход внешнего тактового сигнала.

XTAL2 - Выход инвертирующего усилителя генератора.

Рис.2.1 – Цоколевка микросхемы AT90S8535

2014-02-24

2014-02-24 835

835